## **International Journal of Research Publication and Reviews**

Journal homepage: www.ijrpr.com ISSN 2582-7421

# A Review of Serdes CMOS Transceiver for High Speed Data Transmission

## Ravi Kumar M<sup>1</sup>, Sanjai S<sup>2</sup>, Shilpashree S<sup>3</sup>, Shreyas N Kulal<sup>4</sup> and Tinu M<sup>5</sup>

<sup>1</sup>Assistant Professor, Department of Electronics and Communication Engineering, Cambridge Institute of Technology (CI Tech), Bengaluru, India <sup>2,3,4,5</sup> Student, Department of Electronics and Communication Engineering, CITech, Bengaluru, India DOI: <u>https://doi.org/10.55248/gengpi.5.0324.0706</u>

## ABSTRACT

The development of specialized hardware components to expedite image processing activities is the main goal of the VLSI implementation. These parts consist of memory structures designed for image data, processors tuned for particular algorithms, and specialized accelerators for operations like feature extraction, image filtering, and convolution. In order to enable real-time and resource-efficient applications, high-throughput and low-latency image processing on hardware is the aim.

Keywords: SerDes, Image processing, VLSI, Cadence, Hspice, serialiser, Deserialiser, FPGA

## Introduction

It gets harder to match the timing restrictions of serializers in transmitters due to increasing data rate of serial links. Clock buffers with delay correction can mitigate this problem by synchronizing the clock and data time. Nevertheless, these buffers become sources of noise in the transmitter output and draw a lot of power. The issue is more severe for serializers other than  $2^{n}$ :1, and relying solely on  $2^{n}$ :1 serializers may restrict the design of the system.

SerDes technology is used for high-speed data transfer between various modules and subsystems to provide seamless connection between these VLSI components. The effective serialization and deserialization of data made possible by SerDes integration allows for quick information flow between image sensors, processing units, and memory modules. This method minimizes power consumption, simplifies interconnects, and supports the high data rates required by contemporary image processing applications. Using coaxial or insulated twisted pair cables, serialization and deserialization, long-distance transmission, and other techniques, the SerDes methodology tackles the issues of bandwidth and distance in data transfer.

\*[This paper also discusses image pre-processing methods like noise reduction and contrast enhancement, as well as image collection devices, their dynamic range, calibration, real-time capture, and data output.]\*

Numerous studies have been conducted on the foundations of image processing and picture processing, and the results of these studies have demonstrated a wide range of potential applications in a number of scenarios. Very large scale integration (VLSI)-based solutions are limited, according to a review of the literature. The FPGA offers broad capability that enables programming to your specifications.

NOTE: Can be added to introduction or design challenges

But, like with most things in life, the FPGA's flexibility comes with drawbacks. In this instance, the increased cost, greater internal latency, and reduced analog usefulness are the trade-offs for this versatility.

#### Methodology

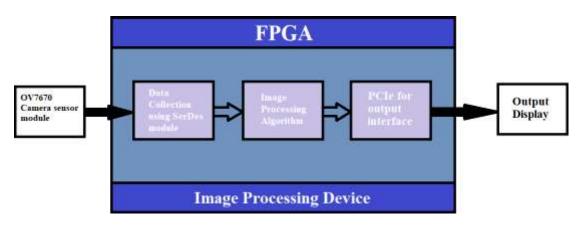

Using a SerDes transceiver to create a serial link instead of a parallel bus is a viable alternative. Since serial link based designs have many benefits over traditional parallel implementations—fewer pins, lower power consumption, smaller connectors, reduced complexity, lower electromagnetic interference, and improved noise immunity—they have been used in off-chip communications for decades. Major SerDes components and basic principles are presented, along with the design flow of a 45nm CMOS process Serializer from unit block design in Cadence Virtuoso to simulation in HSPICE. The process begins with the OV7670 camera sensor module, which captures images in the FPGA image processing device. It involves interfacing the OV7670 camera sensor module with the FPGA to receive the raw image data. The raw data is collected and serialized using a SerDes (Serializer/Deserializer) module. The SerDes module converts parallel data from the camera sensor into a serial stream, which is more efficient for processing and transmission within the FPGA. The serialized image data undergoes various image processing algorithms implemented in the FPGA. These algorithms can include tasks such as filtering, edge detection, and object recognition. Once the image processing is complete, later involves using PCIe (Peripheral Component

Interconnect Express) for the output interface. The processed image data is transferred through PCIe to an external device or host system for further analysis or display. Finally, the output display module receives the processed image data and presents it on a display device for visualization or analysis by the user.

#### Fig 1: Block diagram

#### Literature review

## [1] Eung-ju Kim Member IEEE, Kwan-Jae Lee and Sukki Kim Senior Member IEEE Dept. of Electrical Engineering Korea University, Seoul, Republic of Korea "A HIGH RESOLUTION SERIALIZER AND DESERIALIZER ARCHITECTURE FOR MOBILE IMAGE SENSOR MODULE"

In mobile display applications, the design of high speed interface circuit with low power consumption and small area are the very important technical issues for good system performance. Conventional parallel interface method is less attractive because of pin numbers, electromagnetic interference (EMI) radiation, signal-integrity concerns at higher bus speeds and higher power-consumption profiles. In addition, parallel buses add complexity to routing on the small printed-circuit-board (PCB) footprints in mobile devices. To solve these problems in mobile display applications, special interface technique so called Mobile Display Digital Interface (MDDI) was introduced and used widely now in mobile display applications. Our proposed serializer was designed using multiplexing method. The previous conventional method needs 8 clocks for one 8-bit data packet to make serialized data. But our proposed serializer needs only four clocks by proposed serializer timing controller. To achieve half rate frequency serialization, multiplexing switch should be selected every four cycle of the input clock.

## [2] Taha Mehrabil and Kaamran Raahemifar2 Electrical and Computer Engineering Department Ryerson University Toronto, Canada "Design of a Time Mode SerDes using Differential Pulse Position Modulation (DPPM)" 2017 IEEE 30th Canadian Conference on Electrical and Computer Engineering (CCECE)

Time mode signal processing (TMSP) is the implementation of analog signal processing functions using the most basic element available, namely, propagation delay. Moreover, a time to digital converter (TDC), an important block of time mode circuits, could be used to convert the time difference between two edges of two signals into a sequence of digital numbers.

In this paper, a new time mode SerDes for high data rate chip to chip communication utilizing differential pulse position modulation (DPPM) as the primary method of data encoding was proposed. The proposed design substantiates an improvement in the bandwidth and simplifies the circuit complexity of the currently used serializer de-serializers (SerDes). The complete proposed design was tested in TSMC 65 nm Complementary metal–oxide– semiconductor (CMOS) technology; it achieved a data rate of 5 Gbps running at the input clock frequency of 1.25 GHz. The authors of this paper however, believe that by using a DPPM module only the difference between the original clock and the delayed clock could be sent. This would result in less circuit complexity, greater improvement in bandwidth and further minimization of ISI occurrence. Additionally, there has been abundant research in designing pre-emphasis circuits and decision feedback equalization (DFE) which could be used for reviving the differential pulse position modulated signal at both transmitter and receiver sides respectively

# [3] Image Processing Using FPGAs Donald G. Bailey Department of Mechanical and Electrical Engineering, School of Food and Advanced Technology, Massey University, Palmerston North 4442, New Zealand;

The primary objective of the above mentioned paper is to examine the feasibility and benefits of employing FPGAs for image processing tasks. FPGAs offer the advantage of hardware-level parallelism and reconfigurability, making them suitable for real-time and computationally intensive applications. Discusses how FPGAs provide an opportunity for hardware acceleration of image processing algorithms. Unlike traditional software implementations running on general-purpose processors, FPGAs allow for the parallel execution of tasks, leading to potential performance gains. The paper emphasizes the inherent parallelism in FPGA architectures, enabling the concurrent execution of multiple operations. This parallelism is particularly advantageous

for image processing algorithms that involve repetitive and independent computations on pixel data. The author discusses challenges associated with FPGA-based image processing, including design complexity, resource constraints, and the need for specialized knowledge in FPGA programming. Considerations for overcoming these challenges are likely addressed <sup>[6].</sup>

## [4] A low-noise and fast transient response LDO design for high-speed SerDes Shengyu Song\*, Jianjun Chen, Hengzhou Yuan, Haiyuan Xing and Yi Wen Collage of Computer, National University of Defence Technology, Changsha, 410073, China

The paper emphasizes achieving low-noise characteristics in the LDO design. Noise in the power supply can impact the signal integrity of high-speed SerDes interfaces, and the authors address this challenge by implementing noise reduction techniques in the voltage regulator. A significant focus of the research is on achieving a fast transient response in the LDO design. Fast transient response is essential for quickly adapting to load variations in SerDes circuits, ensuring signal stability during rapid changes in current demand. The LDO design is tailored for applications involving high-speed SerDes interfaces commonly used in data communication, including applications such as high-speed data transmission, communication between links. The potential drawbacks in the paper may include limitations in generalizability, complexity, and cost if the proposed LDO design is highly tailored to specific SerDes requirements, potentially hindering its applicability to diverse scenarios. Trade-offs in performance, insufficient comparison with existing designs, and a narrow scope of validation might affect the overall robustness and practicality of the proposed solution. Additionally, a reliance on simulations without real-world testing and incomplete performance metrics could limit the comprehensiveness of the study, raising concerns about the reliability and applicability of the proposed LDO design in practical high-speed SerDes applicability of the proposed LDO design in practical high-speed SerDes applications.

## Summary of Literature review

#### **TABLE:** Survey summary of serdes implementation

| Serial<br>No. | Author &<br>Year                              | Description                                                                                                                                        | Objective                                                                                                                                           | Methodology                          | Speed &<br>Power                             | Problems                                                       |

|---------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|----------------------------------------------------------------|

| 1             | F. Tobajas et<br>al. (2006)                   | Proposes a low-<br>power, high-<br>resolution SerDes<br>architecture for<br>mobile display<br>applications using<br>multiplexing and<br>DDR.       | Achieve high data<br>rate and low power<br>Consumption for<br>mobile displays.                                                                      | Multiplexing +<br>LVDS               | 2.5 Gbps, Low<br>power                       | Increased complexity, cost.                                    |

| 2             | Taha<br>Mehrabi et al.<br>(2017)              | Explores time mode<br>signal processing and<br>DPPM for chip-to-<br>chip communication,<br>for improved<br>bandwidth and<br>reduced<br>complexity. | Enhance bandwidth<br>and simplify circuit<br>design for chip-to-<br>chip communication.                                                             | Time mode +<br>DPPM                  | High data rate,<br>Low circuit<br>complexity | Minimizing ISI,<br>limitations<br>With data<br>transmission.   |

| 3             | Shengyu<br>Song et al.<br>(2015)              | Designs a low-noise<br>& fast transient<br>response LDO for<br>high-speed SerDes<br>applications, focusing<br>on signal stability.                 | Ensure signal<br>stability and fast<br>response in high-<br>speed SerDes<br>applications.                                                           | LVDS<br>optimization                 | Low noise,<br>Fast transient<br>response     | Generaliz-<br>ability, lack of<br>comprehensive<br>validation. |

| 4             | Chen, F., Wu,<br>J., & Chang,<br>M. F. (2015) | Proposes a 40-Gb/s<br>SerDes interface<br>using transformer-<br>coupled technique for<br>2:1 MUX and 1:2<br>DEMUX.                                 | Achieve 40 Gb/s data<br>transmission with<br>Improved signal<br>integrity using<br>transformer-coupled<br>technique.                                | Transformer-<br>coupled<br>technique | 40 Gb/s,<br>Improved<br>signal integrity     | Circuit complexity,<br>potential crosstalk<br>issues.          |

| 6             | Lee, J. et al.<br>(2015)                      | Designs 56 Gb/s NRZ<br>and PAM4 SerDes<br>transceivers in<br>CMOS.                                                                                 | Design versatile<br>SerDes transceivers<br>capable of high speed<br>(56 Gb/s) and<br>supporting both NRZ<br>and PAM4 formats in<br>CMOS technology. | PAM4 TX: &<br>NRZ<br>encoding        | 56 Gb/s, best operation.                     | High end tool<br>requirement, high<br>power<br>consumption.    |

| 7 |               | Proposes a low-    | Enhance data rate and |                | Higher data |                   |

|---|---------------|--------------------|-----------------------|----------------|-------------|-------------------|

|   | Eung-ju Kim   | power, high-       | reduce power          |                | rate, Lower | Increased         |

|   | et al. (2014) | resolution SerDes  | consumption for       | Multiplexing + | power       | complexity, cost. |

|   |               | architecture for   | mobile display        | DDR            | consumption |                   |

|   |               | mobile display     | applications          |                | compared to |                   |

|   |               | applications       | compared to parallel  |                | parallel    |                   |

|   |               | using multiplexing | interface.            |                | interface   |                   |

|   |               | and DDR.           |                       |                |             |                   |

#### **Conclusion & future scope**

Successful integration of SERDES technology into VLSI design for enhanced data communication in image processing applications. Improved performance metrics such as data transfer rates, latency reduction, and overall system efficiency demonstrated through experimental results. Validation of the proposed methodology for VLSI-SERDES integration in real-time image processing tasks, showcasing its potential for high-performance applications. Future work includes completing other core components of the SerDes, integrating all major blocks into a functioning SerDes system, exploring alternative designs for sub-circuits, optimizing transistor sizing for increased operating frequency, and conducting signal and power integrity analysis to reduce unwanted effects. Validate the VLSI-SERDES integration through simulations and hardware testing to ensure functionality and performance. Measure the data transfer rates, latency, and overall efficiency of the system for image processing tasks.

The use of SerDes technology plays a crucial role in enabling dependable and fast communication among various system components. In designing a Low Dropout (LDO) voltage regulator specifically for high-speed SerDes applications, the paper emphasizes the need of attaining low-noise characteristics and quick transient reactions. The report's case studies and experimental validations offer insightful information on the real-world applications and performance improvements made possible by this integrated methodology. All things considered, the research advances image processing systems by demonstrating how VLSI and SerDes integration may be used to provide real-time, low-latency technologies, and resource-efficient answer for a range of areas.

By sampling input on both positive and negative clock edges, the Deserializer provides a more precise and efficient serialization process. There is no longer a need for an extra latch or 2:1 MUX because to the more precise and efficient design of the proposed Serializer and Deserializer. The significance of comprehending the fundamental elements of a SerDes system and the serialization process for effective high-speed circuit design and execution is emphasized in the thesis' conclusion.

### REFERENCES

- [1] F. Tobajas, R. Esper-Chain, R. Regidor, O. Santana and R. Sarmiento, "A Low Power 2.5 Gbps 1:32 Deserializer in SiGe BiCMOS Technology," 2006 IEEE Design and Diagnostics of Electronic Circuits and systems, Prague, Czech Republic, 2006, pp. 19-24, doi: 10.1109/DDECS.2006.1649564

- [2] E. -j. Kim, K. -J. Lee and S. Kim, "A high resolution Serializer and Deserializer architecture for mobile image sensor module," CCECE 2010, Calgary, AB, Canada, 2010, pp. 1-4, doi: 10.1109/CCECE.2010.5575153.

- [3] F. -T. Chen, J. -M. Wu and M. -C. F. Chang, "40-Gb/s 0.7-V 2:1 MUX and 1:2 DEMUX with Transformer-Coupled Technique for SerDes Interface," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 4, pp. 1042-1051, April 2015, doi: 10.1109/TCSI.2015.2395634

- [4] Lee, Jri, et al. "Design of 56 Gb/s NRZ and PAM4 SerDes transceivers in CMOS technologies." IEEE Journal of Solid-State Circuits 50.9 (2015): 2061- 2073.

- [5] Taha Mehrabi1 and Kaamran Raahemifar2 Electrical and Computer Engineering Department Ryerson University Toronto, Canada "Design of a Time Mode SerDes using Differential Pulse Position Modulation (DPPM)" 2017 IEEE 30th Canadian Conference on Electrical and Computer Engineering (CCECE).

- [6] A. A. Hafez, M.-S. Chen, C.-K. K. Yang, "A 32-48 Gb/s serializing transmitter using multiphase serialization in 65 nm CMOS technology," IEEE J. of Solid-State Circuits (JSSC), vol. 50, no. 3, pp. 763-775, Mar. 2015.

- [7] Y. -U. Jeong, J. -H. Chae, S. Choi, J. Yun, S. -H. Jeong and S. Kim, "A Low-Power and Low-Noise 20:1 Serializer with Two Calibration Loops in 55- nm CMOS," 2019 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), Lausanne, Switzerland, 2019, pp. 1-6, doi: 10.1109/ISLPED.2019.8824879.