**International Journal of Research Publication and Reviews**

Journal homepage: <u>www.ijrpr.com</u> ISSN 2582-7421

# Design of on Chip Permutations Network using 3D Mesh Network on Chip

# <sup>1</sup>Yeleti Srivarshini, <sup>2</sup>Dr B Ramana Kumar

<sup>1</sup>Research Scholar, Department of ECE, International School of Technology and Sciences (Women), Affiliated to JNTUK, NH-16, East Gonagudem, Rajanagaram, Rajamahendravaram, Andhra Pradesh 533294, India.

<sup>2</sup>Associate Professor, Department of ECE, International School of Technology and Sciences (Women), Affiliated to JNTUK, NH-16, Eastgonagudem, Rajanagaram, Rajamahendravaram, Andhra Pradesh 533294, India.

#### ABSTRACT

The network on chip (NoC) due to their flexibility, scalability and high bandwidth features they are considered as on-chip communication fabrics for future multiprocessor system on chips(MPSOCs). In my abstract the design of a network on chip to support a guaranteed throughput is explained. The clos network topology is used with the three stages of switches of 4ports of inputs and outputs. This network is designed to support a guaranteed traffic permutation in multiprocessor system-on-chip applications. The proposed network employs a pipelined circuit-switching approach combined with a dynamic path-setup scheme enables runtime path arrangement for arbitrary traffic permutations. Network on chip (NoC) is a communication subsystem on a integrated circuit, typically between IP cores in a system on a chip(SoC).

## I. Introduction

Multiprocessor systems-on-chips (MPSoCs) have emerged in the past decade as an important class of very large scale integration (VLSI) systems. An MPSoC is a system on- chip a VLSI system that incorporates most or all the components necessary for an application that uses multiple programmable processors as system components. MPSoCs are widely used in networking, communications, signal processing, and multimedia among other applications of parallel processing, scientific computing, and so on. The empirical law of Moore does not only describe the increasing density of transistors permitted by technological advances. It also imposes new requirements and challenges. Systems complexity increases at the same speed. Now a day's systems could never be designed using the same approaches applied 20years ago. New architectures are and must be continuously conceived. It is clear now that Moore's law for the last two decades has enabled three main revolutions. To overcome the drawback of packet switching and fixed arbitrary scheme for arbiter in switch circuit, a new design is proposed with configurable and programmable Arbiter for runtime traffic permutation. The main drawback previous system is with the Arbitration schemes. To overcome these problems we are using run time programmable arbiter in each switch. The Arbiter is programmed with new Arbitration schemes by overcoming drawbacks of previous schemes. The efficiency is improved. The proposed system re-routes data on erroneous links to a set of spare wires without interrupting the data flow. The main advantage of Circuit Switching is manual establishment of dedicated channel, with a fixed delay for data transaction

# **II. LITERATURE REVIEW**

Technological evolution enables the integration of billions of transistors on a chip. This allows an efficient exploitation of resources and increasingly complex and varied design. The Multiprocessor Systems on Chip (MPSoC) represent a new paradigm emerged from this development. They can include several heterogeneous components like processors (Scalar, Risk) memories, hardware accelerators (DMA, DCT, FFT) and peripheral input/ output. The communication between these various components is provided by an interconnection network called Network on Chip (NoC). Performance evaluation is a key step in any MPSOCs design and especially of the selected communication architecture, allowing for decisions and trade-offs in view of system. The survey presents a perspective on the existing research and practices initiated for the Design Space Exploration (DSE) in Multiprocessor System on Chip (MPSoC) technology Reduction in size as well as adding more functionality within a single chip by incorporating multiple processors remains the key in the development of the modern MPSoC.

This rapid development has been made possible because of the techniques used for scaling down the size of the chip in the field of integrated circuits. MPSoC has been considered as the best candidate for applications such as networking, telecommunication, multimedia, etc. which require high computational demand, high performance, flexibility, high energy efficiency, and low cost design. The designers have the onerous task of building

MPSoCs for such applications because they have huge design options in terms of Processing Elements (PEs), micro-architectural features, interconnects, etc. to be considered with specific constraints.

Geoffrey Blake, Ronald G. Dreslinski, and Trevor Mudge carried out survey on multi core processors. Survey also discusses on architectural classifications, advantages by using multi core systems so that the performance can be increased by increasing number of cores rather than frequency. With the emergence of commercial multi core architectures in an array of application domains, it is important to understand the major design characteristics common among all multi cores. Survey defined five major attributes common among multi core architectures and discussed the tradeoffs for each attribute in the context of actual commercial products. These areas were application domain, power/performance, processing elements, memory, and accelerators/integrated peripherals.

B. Neji, Y. Aydi, R. Ben-atitallah, S. Meftaly, M. Abid, J-L. Dykeyser carried out survey on multistage interconnect network for MPSoC. It also tells that multistage network is well suited for MPSoC. It also estimates performance in terms of area, latency and power consumption. It also discuss on topology, routing algorithm and technical arbitration, By taking a prototyping on FPGA, compares other type of networks in terms of performance.

# III. MULTIPROCESSOR SYSTEM ON CHIP

Multiprocessor systems on chip (MPSoC) are the latest materialization of Very large scale integration (VLSI) technology. A single Integrated Circuit can contain over 100 million transistors and international technology road map for semiconductors predicts that chips with billion transistors are within reach. Harnessing all this raw computing power requires designers to move beyond logic design into computer architecture. The demands placed on these chips by applications require designers to face problems not confronted by traditional computer architecture. Real time deadlines, very low power operation and so on. These opportunities and challenges make MPSoC design an important field of research.

A Soc is an integrated circuit that implements most or all of the functions of a complete electronic system. The most fundamental characteristic of anSoC is complexity A memory chip may have many transistors, but its regular structure makes it a component and not a system. Exactly what components are assembled on the Soc varies with the application. Many SoC's contain analog and mixed-signal circuitry for input/output (I/O). Although some high-performance I/O applications require a separate analog interface chip that serves as a companion to a digital Soc, most of anSoc is digital because that is the only way to build such complex functions reliably. The system may contain memory, instruction-processors (central processing units), specialized logic, buses, and other digital functions. The architecture of the system is generally tailored to the application rather than being a general purpose processors.

## **IV. MULTISTAGE INTERCONNECTION NETWORK**

The Processing Elements (PE's) previously described are mostly interconnected by a Network-on-Chip (NoC). A NoC is composed of Network Interfaces (NI), routing nodes and links. The NI implements the interface between the interconnection environment and the PE domain. It decouples computation from communication functions. Routing Nodes, also called routers, are in charge of routing are arbitrating the data between the source and destination PEs through the links. Several network topologies have been studied.

#### 4.1 An Introduction to Interconnection Networks

Much of the early work on interconnection networks was motivated by the needs of the communications industry, particularly in the context of telephone switching. With the growth of the computer industry, applications for interconnection networks within computing machines began to become apparent.

Among the rest of these was the sorting of sequences of numbers, but as interest in parallel processing grew, a large number of networks were proposed for processor to memory and processor to processor interconnection. With the advent of the fast packet switch, interest in interconnection networks has turned full circle in that many of the networks originally proposed for parallel processing are now being considered for use in fast packet switch designs. Machines began to become evident.

#### 4.2 Control Mechanism

Interconnection networks may also be classified according to the control mechanism employed to connections between input ports and output ports. If the algorithm is centralised and implemented in a central processor then the state of all existing connections and all connection requests may be consulted in order to make the necessary routing decisions. The use of a centralised control mechanism implies circuit switching where the holding time of a connection is much greater than the time required to establish connection. The vast majority of modern telephone switch designs use centralised control. In fast packet switching applications the control mechanism must be distributed across the switch fabric and must be capable of operating without access to information regarding the entire state of the switch.

#### V. DESIGN APPROACH

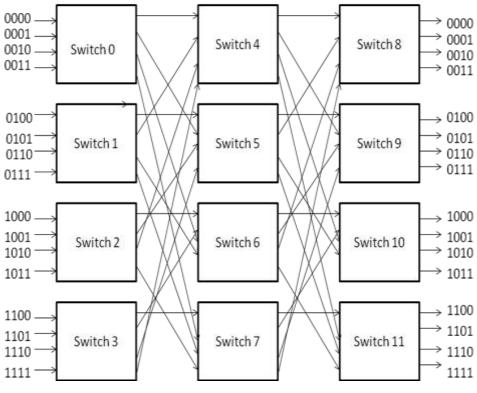

#### Proposed on chip network topology

The design of multistage switching on chip network topology with pipelined circuit switching with dynamic path, the dynamic path-setup scheme enables runtime path arrangement for arbitrary traffic permutations. The circuit-switching approach offers a guarantee of permuted data. The proposed design involves configuration and programming of Arbiter in switch circuit

#### Figure 5.1: Proposed on-chipnetwork topology with portaddressing schem

## VI. VERILOG HARDWARE DESCRIPTION LANGUAGE

A Hardware Description Language is a language used to describe a digital system, for example, a computer or a component of a computer. One may describe a digital system at several levels. For example, an HDL might describe the layout of the wires, resistors and transistors on an Integrated Circuit (IC) chip, i.e., the switch level or, it might describe the logical gates and flip flops in a digital system, i.e., the gate level. An even higher level describes the registers and the transfers of vectors of information between registers. This is called the Register Transfer Level (RTL). Verilog supports all of these levels. However, this handout focuses on only the portions of Verilog which support the RTL level.

Verilog is one of the two major Hardware Description Languages (HDL) used by hardware designers in industry and academia. VHDL is the other one. The industry is currently split on which is better. Many feel that Verilog is easier to learn and use than VHDL. As one hardware designer puts it, "I hope the competition uses VHDL." VHDL was made an IEEE Standard in 1987, while Verilog is still in the IEEE standardization process.

## Popularity of Verilog HDL

Verilog HDL has evolved as a standard hardware description language. Verilog HDL offers many useful features

- Verilog HDL is a general-purpose hardware description language that is easy to learn and easy to use. It is similar in syntax to the C programming language. Designers with C programming experience will find it easy to learn Verilog HDL.

- Verilog HDL allows different levels of abstraction to be mixed in the same model. Thus, a designer can define a hardware model in terms of switches, gates, RTL, or behavioural code. Also, a designer needs to learn only one language for stimulus and hierarchical design

#### VII. SIMULATION AND SYNTHESIS TOOLS

## 7.1 ModelSim

ModelSim is a verification and simulation tool for VHDL, Verilog, System Verilog, and mixed language designs. It is divided into four topics, which you will learn more about in subsequent lessons. • Basic simulation flow. • Project flow. • Multiple library flow. • Debugging tools.

Basic Simulation Flow The figure.7.1 shows the basic steps for simulating a design in ModelSim. Creating the Working Library in ModelSim, all designs are compiled into a library. You typically start a new simulation in ModelSim by creating a working library called "work," which is the default library name used by the compiler as the default destination for compiled design units.

- Compiling Your Design After creating the working library, you compile your design units into it. The ModelSim library format is compatible

across all supported platforms. You can simulate your design on any platform without having to recompile your design.

- Loading the Simulator with Your Design and Running the Simulation With the design compiled, you load the simulator with your design by invoking the simulator on a top-level module (Verilog). Assuming the design loads successfully, the simulation time is set to zero, and you enter a run command to begin simulation.

- Debugging Your Results if you don't get the results you expect, you can use ModelSim's robust debugging environment to track down the cause of the problem

# VIII SIMULATION RESULTS

8.1: Top module 3stage switching circuit:

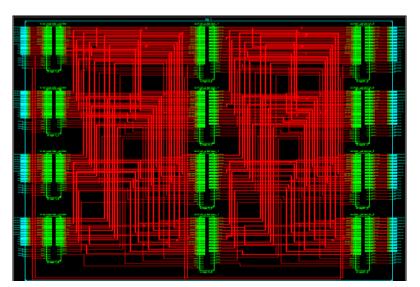

Figure8.1:Top module 3stage switching circuit

#### 8.2: ARBITER

| <b>į</b> .                                                                                | Msgs                 |         |        |        |   |   |   |   |   |   |   |   |

|-------------------------------------------------------------------------------------------|----------------------|---------|--------|--------|---|---|---|---|---|---|---|---|

| <ul> <li>/round_robin/dk</li> <li>/round_robin/rst</li> <li>/round_robin/start</li> </ul> | 1'h1<br>1'h0<br>1'h0 |         |        |        |   |   |   |   |   |   |   | - |

| 🖅 🌢 /round_robin/request_vector                                                           | 111100               | (111100 |        | 001101 |   |   |   |   |   |   |   |   |

| 0-4 /round_robin/current_master                                                           | 2                    | 0       | 1      |        | 3 | 0 | 2 | 3 | 0 | 2 | 3 | 0 |

| 0-4/ /round_robin/i                                                                       | 32/b0000000          | -       | 32'h0( | 000000 |   |   |   |   |   |   |   |   |

#### Figure 8.2.1: Simulation results for Round Robin

| <ul> <li>/ic_tb/clk</li> <li>/ic_tb/rst</li> </ul>  | 1<br>0         |       |   |      |     |      |         |      |               |       |       |                |       |     |

|-----------------------------------------------------|----------------|-------|---|------|-----|------|---------|------|---------------|-------|-------|----------------|-------|-----|

| <pre>/ic_tb/req_in /ic_tb/status /ic_tb/grant</pre> | 1<br>0111<br>1 | ,0000 |   |      |     |      | 24<br>2 |      | 1100<br>sim:/ | /ic t | b/sta | 11110<br>tus ( | 3 150 | ns  |

| /ic_tb/ans_out                                      | 00             | 00    | 1 |      | 1   |      |         |      | 0000          |       | w     |                | 0     |     |

| 🖬 🥠 /ic_tb/ans_in                                   | 00             | 00    |   | 1    |     |      |         | 10   | 100           |       |       | 10             | 00    |     |

| 🗉 🔶 /ic_tb/req_bus                                  | 111            | 000   |   | 1001 | 011 | 1101 | 1111    | 1000 | 1             | 001   | 1011  | 1000           | 1     | 001 |

#### Figure 8.2.2:Simulation results for input circuit

| //tond_priority/dli<br>//tond_priority/rit | 2110        | -    |          | -   | 7    |   |       |             |          |          |         |           |        |         |

|--------------------------------------------|-------------|------|----------|-----|------|---|-------|-------------|----------|----------|---------|-----------|--------|---------|

| A flood pounty/statt                       | 190         | -    |          |     |      |   |       |             |          |          |         |           |        |         |

| Itel prosty/program_pro                    |             |      |          | -   |      |   | <br>_ |             |          |          |         | _         |        |         |

| 0.4 /towd_psuity/sailer_said               | Dec II      | 2    | 11       | 12  | 23   | _ | <br>  |             |          |          |         | -         |        |         |

| D.# /fixed_prouts/prontly                  | 12          | .0   | 14       | 116 | ) 32 | _ | <br>_ | Charlen and |          |          |         |           |        |         |

| 3 / fixed_priority/request_vect            | pr 010110   | .111 | 111      | _   |      |   |       | Loopti      | 1 [1111  | 1 )0:0:  | 10      | 111000    | 110000 | 030000  |

| D / freed_procety/carried_med              | 1           | 0    |          |     |      |   |       | 3           | 1        | 3        | 1       |           | 3      | (5      |

| C*                                         | Vetter 1    |      |          | -   |      |   |       | 32          | 4        | 32       | 14      | 1         | 32     | (9      |

| C-4 /head_priority/master                  | 1           | 1000 |          | -   |      |   |       | 3           | 1        | 3        | 1       |           | 3      | 15      |

| C /twee priority/                          | E0000000E   | 327  | 00000006 |     |      |   |       | 32%0000     | 32'10000 | 32'50800 | 32h0005 | 325600000 | 01     | 3250008 |

| D. (Towd_prioticy)                         | 32100000006 |      | 0.00000  |     |      |   | 1     | 3210000000  | 16       |          | -       |           |        |         |

#### Figure 8.2.3: Simulation results for fixed priority

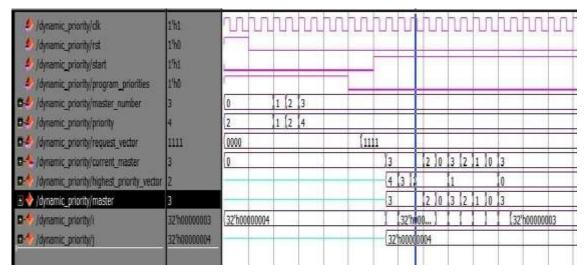

Figure 8.2.4: Simulation results for dynamic priority

| * /etermadate_nettr_ft/da                | 1                               |        |   |   | - |        | 1 |   | - |     |     | 1 |   |

|------------------------------------------|---------------------------------|--------|---|---|---|--------|---|---|---|-----|-----|---|---|

| * (vitermediate nettati Ustrat           | -                               |        |   |   |   |        |   |   |   |     | - 1 |   |   |

| C-* /vitermediate_switch_th/in0          | 17me                            | 8'haa  |   |   |   |        |   |   |   |     | -   |   |   |

| D- /attarmediate_switch_th/w1            | #7688                           | 6'hbb  |   |   |   |        |   |   |   |     |     |   |   |

| D 4 /with maddette_switch_th/w2          | #Thee                           | Bhoc   |   |   |   |        |   |   |   |     |     |   |   |

| D 4 //etarmediata_switch_th/es3          | 8344                            | fi'hdd |   |   |   |        |   |   |   |     |     |   |   |

| D * //witermediate_switch_th/addr_mil    | a'hue                           | Shaa   |   |   |   |        |   |   |   |     |     |   |   |

| 0-% /intermediate_switch_th/addr_m1      | #bbb                            | S'hbb  |   |   |   |        |   |   |   |     |     |   |   |

| D-5 / intermediate_switch_tb/addr_in2    | Whee                            | B'hcc  | _ |   | _ |        |   |   | _ |     | _   | _ | _ |

| D 🔨 / #thermaidiata_savitch_th/addr_in3  | 87646                           | 6'hdd  | - |   |   |        | - |   |   |     |     |   |   |

| Cl-* /attermediate_switch_th/out0        | a'huu                           | £/h00  |   |   | _ | a'han  |   | _ | _ |     |     | _ |   |

| O / Mermelane_switch_th/out1             | @Thinks                         | 8'h00  |   |   |   |        | - |   | _ | _   |     | _ | _ |

| C-* /Vitermediate_switch_tb/0x82         | WNOT                            | 8'600  | _ | _ | _ |        | - | _ | _ |     | _   | _ | _ |

| D-5 / Hermediate_switch_tb/out3          | 87502                           | B'h00  | _ | _ | _ |        | - | _ | _ | _   | _   | _ | _ |

| C (#itermediate_sevilch_th/addr_sutt     | 87.08                           | B'h00  |   |   | _ | la'haa | - |   | _ |     | -   | _ | _ |

| D * / entermediane_sewitch_th/ieldr_sul1 | a'hith                          | 6,000  | - | - | _ |        | - |   | _ | _   | _   | _ | _ |

| D //wiermestaris_switcb_ttl/adut_sut2    | 8766                            | s'h00  |   | - | _ |        | - |   | _ |     | _   | _ | _ |

| C-* / intermediate_switch_tb/addr_out3   | 8'808                           | 8/100  |   | - | _ |        | - | _ | _ | -   | _   | _ | _ |

| /vitermediate_switch_th/req_init         | 1. Contraction (1. Contraction) |        |   |   |   |        |   |   |   | 1.1 | _   |   |   |

| /vitermediate_switch_th/req_int          | <u>#</u>                        |        |   |   |   |        |   |   |   |     |     |   |   |

| /attermediate_seatch_th/reg_st2          | 0                               |        |   | - | _ |        | - | _ | _ |     | _   | - | _ |

| /intermediate_switch_tb/req_is3          | 1                               |        |   |   |   |        |   |   |   |     |     |   |   |

## Figure 8.2.5: Simulation results for intermediate switch

| /switch_address_ttp/dk            | 1711  |       |    |      |        |

|-----------------------------------|-------|-------|----|------|--------|

| /switch_address_tb/mt             | 170   |       |    |      |        |

| D 1 /switch_address_tb/in0        | Shaa  | 8'haa |    |      |        |

| D-4 /metch address th/m1          | #Thbb | Shbb  |    |      |        |

| D-5 /switch_address_tb/in2        | Bhoc  | 8'hcc |    |      |        |

| D-1 /switch address tb/in3        | STIdd | 8'hdd |    |      |        |

| D-% /switch_address_tb/addr_in0   | Fhaa  | Shaa  |    |      |        |

| D-1 /writch address th/addr m1    | White | 8'hbb |    |      |        |

| D-4 /switch address th/addr in2   | STICC | 8'hoc |    |      |        |

| D-* /witch_address_tb/addr_m3     | Shdd  | 8 bdd |    |      |        |

| D-4 /switch address th/dent addr0 | 2760  | 2'h0  |    |      |        |

| D / jewitch_address_th/dest_addr1 | 271   | 2'h1  |    |      |        |

| D-5 /switch_address_tb/dest_addr2 | 272   | 2'h2  |    |      |        |

| /switch_address_tb/reg_in0        | 1     |       |    |      |        |

| /switch_address_tb/reg_ml         | 4     |       |    |      |        |

| /switch_address_th/req_in2        | 0     |       |    |      |        |

| /switch_address_tb/req_in3        | 1     |       |    |      |        |

| D-5 /switch_address_tb/dest_addr3 | 213   | 2h3   |    |      |        |

| D / /switch_address_tb/out0       | STiaa | 8'h00 | .8 | 'haa |        |

| D-% /switch_oddress_tb/out1       | STIDD | 8'h00 |    |      | s'hbb  |

| D-5 /switch_address_th/out2       | 87600 | 8'500 |    |      |        |

| D 4 /switch_address_tb/out3       | 8'hdd | 8'h00 |    |      | 18'hdd |

# Figure 8.2.6: Simulation results for switch address

| /top/reg_ind_0    | 1%1  |   |   |   |   |   |   |   |   |   |   |   |       |   |   |   | - |   |

|-------------------|------|---|---|---|---|---|---|---|---|---|---|---|-------|---|---|---|---|---|

| /top/cet_int_0    | 131  |   |   |   |   |   |   |   | - |   |   |   |       |   |   |   | - |   |

| 1 /top/reg_in2_0  | 1'h1 |   |   |   |   |   |   |   |   |   |   |   |       |   |   |   |   |   |

| 4. /top/req_in3_0 | 191  |   |   |   |   |   |   |   |   |   |   |   |       |   |   |   |   |   |

| /mp/reg_in0_1     | 170  |   | _ |   | _ |   |   |   |   |   |   |   | <br>  |   |   |   |   |   |

| /top/rest_init_1  | 196  |   |   | _ |   | - | - | _ |   |   | - |   |       |   | _ | - |   |   |

| 1 /up/reg_in2_1   | 1/10 | - | _ | _ |   | _ |   |   |   |   |   |   |       |   |   |   | _ |   |

| /top/reg_mil_1    | 1'60 | _ |   |   | _ |   |   |   |   |   |   |   |       |   |   |   |   |   |

| 1/top/reg_in0_2   | 110  |   |   |   |   | - |   | - |   |   |   |   | <br>_ |   | _ | _ | _ |   |

| 1/top/reg_int_2   | 1911 |   |   | _ |   |   |   |   | - |   |   |   |       |   |   | - |   |   |

| 4 /mp/reg_in2_2   | 1.90 |   |   |   |   |   |   |   |   | _ |   | _ |       | _ | _ | _ |   |   |

| 1 /top/reg_ing_2  | 170  |   |   |   |   |   |   |   |   |   |   |   |       |   |   |   |   |   |

| /top/ceq_in0_3    | 120  |   | _ |   |   | _ | _ | - |   |   |   |   | <br>_ | _ | _ | _ | _ | _ |

| 1/mp/red_int_3    | 1'50 |   |   | _ |   |   |   |   |   |   |   |   | <br>  |   |   |   |   |   |

| /top/reg_in2_3    | 1'00 |   |   |   |   |   |   |   |   |   |   |   |       |   | - |   |   |   |

| E_Eni_pervent     | 170  |   |   |   |   |   |   |   |   |   |   |   |       |   |   |   |   |   |

Figure 8.2.7: simulation results for part1 of ocp

| /top/ck        | 3703   | ากการการการการการการการการการการการการกา |

|----------------|--------|------------------------------------------|

| 4 /top/std     | 170    |                                          |

| 0_0/in0_0      | 8761   | 8'ha1                                    |

| 0.4 /top/in1_0 | 8'ha2. | 3'ha2                                    |

| D-4 /tnp/in2_0 | 8°ha3  | a'hag                                    |

| 0-4 /top/in3_0 | 8'004  | 8'ha4                                    |

| 11 /inp/in0_1  | 8765   | 8'ha5                                    |

| D-1 /100/m1_1  | B'hat. | ,8'haō                                   |

| D 4 /top/in2_1 | U'ha7  | 8'he7                                    |

| D 4 /top/in3_1 | 8708   | 8'ha8                                    |

| E_0ni/qat/ 100 | 8'ha9  | (a'ha9                                   |

| D 4 /top/in1_2 | Shat   | a'hao                                    |

| 0-4 /top/in2_2 | 5700   | a'haa                                    |

| D-4 /mp/m3_2   | Wheb   | 3'hab                                    |

| E_0ni/qot/ 40  | S'hec  | 8'hac                                    |

| 0.4 /top/in1_3 | #'hed  | 8'had                                    |

| D# /10p/in2_3  | 8'%ae  | 8'hae                                    |

| Cd /top/inj 3  | B75af  | ,8'haf                                   |

#### Figure 8.2.8:simulation results for part2 of ocp

| D.4 /mp/ans.out.3.     | 2'h0.    | 2'h0   |        |         |       |         |  |  |

|------------------------|----------|--------|--------|---------|-------|---------|--|--|

| S_(top/ans_suit)_2     | 230      | 230    |        |         |       |         |  |  |

| D - /mp/out0_0_2       | R'haz    | 89,00  | 16'hai |         |       |         |  |  |

| D - /mp/0ull1_0_2      | 87509    | a'h00  |        |         |       |         |  |  |

| B 4 /00p/out2_0_2      | 11'509   | 87600  |        |         |       |         |  |  |

| CI-100/0013_0_2        | 81108    | 8'7:00 |        |         |       |         |  |  |

| th / / http://out0_1_2 | 906.8    | 8'000  |        |         |       |         |  |  |

| D-1 /top/out1_1_2      | 8'000    | 8'h/00 |        |         |       |         |  |  |

| D & /top/out1_1_2      | #'hog    | 00yf?B |        | 10,7649 |       |         |  |  |

| D 1 /mp/md3_1_7        | 11*INO11 | 81000  |        |         |       |         |  |  |

| 0-4 /top/out0_2_2      | a'b00    | 8'7:00 |        |         |       |         |  |  |

| 1 /top/out1_2_2        | #*b00    | 8'100  |        |         |       |         |  |  |

| D-4- /top/out2_2_2     | 6'000    | 8'h00  |        |         |       |         |  |  |

| D-1-/IBp/out3_2_2      | 3.906.8  | 8'h00  |        |         |       |         |  |  |

| C. 2.,0hun/math, -> 0  | d'faiet  | 8'b00  |        |         |       | Xii'ha4 |  |  |

| ± 1 /top/out1_7_2      | 6'ha3    | 81600  |        |         | Lubal |         |  |  |

| C /wp/ock2_3_2         | 8'562    | 8'h00  |        | 18/08/2 |       |         |  |  |

| D-4 /100/0053_3_3      | 8'509    | 8'100  |        |         |       |         |  |  |

### Figure 8.2.9: simulation results for part3 of ocp

# IX CONCLUSION

Project designed NOC: onchip network designed supporting traffic permutations in MPSoC applications. By using a circuit-switching approach combined with dynamic path-setup scheme under a Closed network topology, the proposed design offers arbitrary traffic permutation in runtime with compact implementation overhead.

By using Closed Network Topology we can operate network at a range of approx: 100MHz frequency, bandwidth of approx: 30Gbps.

By using Circuit Switching technique we can have a dedicated path delay from source Node to Destination Node Link once established is serviced till all amount transactions is carried out.

EPB: Exhaustive profitable Backtracking is the routing technique used in setting up the link for data communication.

Dynamic path setup plays a major role in probing, forsetting link.

#### **Future scope**

Network On Chip link share Self Switching & Cross Coupling Capacitance nets ,due to this nets consume power.

For optimizing the dynamic power consumption we use an Encoding technique called Bus-Invert method.

#### References

- 1. L. Benini and G. De Micheli, "Networks on chips: A new SoC paradigm," IEEE Computer, vol. 35, no. 1, pp. 70–78, Jan. 2002.

- K. Goossens, J. Dielissen, and A. Radulescu, "Æthereal network on chip: Concepts, architectures, and implementations," IEEE Des. Test. Comput., vol. 22, no. 5, pp. 414–421, 2005.

- 3. S. Borkar, "Thousand core chips—A technology perspective," in Proc.ACM/IEEE Design Autom. Conf. (DAC), 2007, pp. 746–749.

- 4. P.-H. Pham, P. Mau, and C. Kim, "A 64-PE folded-torus intra-chip communication fabric for guaranteed throughput in network-on-chip based applications," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), 2009, pp. 645–648.

- C. Neeb, M. J. Thul, and N. Wehn, "Network-on-chip-centric approach to interleaving in high throughput channel decoders," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), 2005, pp. 1766–1769.

- H. Moussa, A. Baghdadi, and M. Jezequel, "Binary de Bruijn on-chip network for a flexible multiprocessor LDPC decoder," in Proc. ACM/IEEE Design Autom. Conf. (DAC), 2008, pp. 429–434.

- H. Moussa, O. Muller, A. Baghdadi, and M. Jezequel, "Butterfly and Benes-based on- chip communication networks for multiprocessor turbo decoding," in Proc. Design, Autom. Test in Euro. (DATE), 2007, pp. 654–659.

- S. R. Vangal, J. Howard, G. Ruhl, S. Dighe, H. Wilson, J. Tschanz, D. Finan, A. Singh, T. Jacob, S. Jain, V. Erraguntla, C. Roberts, Y.Hoskote, N. Borkar, and S. Borkar, "An 80-tile sub-100-w TeraFLOPS processor in 65-nm CMOS," IEEE J. Solid-State Circuits, vol. 43, no.1, pp. 29– 41, Jan. 2008.

- 9. W. J. Dally and B. Towles, Principles and Practices of Interconnection Networks:. San Francisco, CA: Morgan Kaufmann, 2004.

- N. Michael, M. Nikolov, A. Tang, G. E. Suh, and C. Batten, "Analysis of application- aware on-chip routing under traffic uncertainty," in Proc. IEEE/ACM Int. Symp. Netw. Chip (NoCS), 2011, pp. 9–16.