## **International Journal of Research Publication and Reviews**

Journal homepage: www.ijrpr.com ISSN 2582-7421

# **Relative Study and Design of CSRO in 16 nm Technology**

N. Jyothsna<sup>1</sup> K. Rajesh<sup>2</sup>, S. Sameer Basha<sup>3</sup>, A. Sai pranith<sup>4</sup>, Y. Chandra Sekhar<sup>5</sup>

<sup>1</sup>Assistant Professor, ECE Department, Santhiram engineering college, Nandyal, AP, India. <sup>2,3,4,5</sup>Student, ECE Department, Santhiram engineering college, Nandyal, AP, India.

#### ABSTRACT

This research examines the performance of phase noise and the tuning range of ring oscillator design (ROs). Comparisons between the planned circuits and power consumption and frequency of the current architecture. Maximum frequency, power delay product, phase noise, and bandwidth (PDP) PNBP, too. Three-stage CSROs have been used for performance evaluation. Use of the 16 nm PTM High in Cadence software Technology model for performance (HP). Results from simulations show that one NMOS sink or two newly suggested CSRO designs. In terms of PDP and PNBP, PMOS sources produce identical optimal outcomes as the current CSRO employing a switch output system, a benefit of lower necessary area All four proposed architectures exhibit enhanced compared to the traditional, performance in terms of PDP and PNBP CSRO. Additionally observed and compared was the CSROs' performance.

Keywords: CSRO, PNBP, PDP,16nm Technology

## 1. INTRODUCTION

In contemporary RF wireless communication systems, the voltage regulated oscillator (VCO) is one of the most crucial building parts. The two primary types of RF VCOs are ring oscillators and LC VCOs. Considering that the quality factor (Q) of Higher oscillation frequency and better phase noise are features of the LC tank and LC VCO.performance. However, the on-chip variable capacitors and the changeable range of the on-chip integrating capacitors are what provide the LC VCO's frequency adjusting capability. Constrained, which causes the LC VCO's frequency adjustment range to be quite small. Additionally, the use of several on-chip inductors results in a comparatively high chip area of an LC VCO The ring is another superior option for the installation of RF VCOs. Oscillator. The design theory for current-mode oscillators states that current-mode oscillators typically have distinct characteristic equations, and it is quite simple to determine their oscillation conditions and oscillation frequencies from these equations. However, the claimed current-mode oscillators' oscillators requires are quite low. low, have oscillation frequencies of less than 100 MHz, and are challenging to in relation to contemporary high-frequency communication technologies. The purpose of this study is the development of RF ring oscillators using low frequency oscillator technologies now in use.

RF ring oscillators of the new generation have precise characteristic equations. oscillation frequency and condition, and it is simpler and more practical. than the RF ring oscillator technique that is more common. A RFQRO for the L-band, for instance By joining delay cells into a ring, RF ring oscillators are created, and the delay cells are the components of RF ring oscillators that are most crucial. Fig. 1 shows a typical delay cell. and it has 11 MOS transistors in it. The phase shift is achieved by three identical delay cells. not respectable, The three-stage ring oscillator also lacks any distinguishing features. equation, the typical RF ring, the oscillation condition, and the frequency of the oscillation. Oscillators don't show the theory of design

Applications for wireless communication are created to test the viability of using the RF ring oscillator design using the current-mode approach. Currentmode low frequency oscillators and RF ring oscillators are used in the implementation. By incorporating delay cells into a network, Level RF ring oscillators can operate more efficiently. In RF ring oscillators, the most crucial components are the ring and the delay cells. Current-mode low frequency oscillator theory is used to design RF ring oscillators. another superior option for RF VCO design, which will simplify RF ring design oscillators are more simple and practical. The CMOS technology makes it feasible to match noise and power simultaneously.

## 2. APPROACH

#### 2.1 01-V 0.25- µW Inverter Stacking Amplifier With 1.07 Noise Efficiency Facto

Very power-efficient amplifier is shown in this study. The suggested amplifier achieves six-time current reuse by stacking inverters and dividing the capacitor feedback network, considerably enhancing the trans conductance and decreasing noise without increasing current consumption. In order to provide reliable operation under a 1-v supply, an unique biasing mechanism is developed. A 180-nm CMOS prototype has the best noise efficiency factor of 1.07 among known amplifiers with 5.5-v rms noise within 10-khz BW while using only 0.25-w of power.

#### 2.2 0.13-µmCMOS PCSNIM LNA formultistandard 0.9, 1.8, and 2.1GHz mobile application.

This research focuses on the design of a fully integrated PCSNIM LNA, a 0.13-m CMOS multi-standard low-noise amplifier with power constraints. CMOS switches are used to implement the multi-standard capabilities. When compared to the current multi-standard LNA topologies, this approach is unusual in that the input and output matching are entirely implemented on a chip. Operating frequencies for the multi-standard LNA include 0.9, 1.8, and 2.1 GHz. The design included GSM900, DCS1800, and W-CDMA applications for wireless technologies. The multi-standard LNA can achieve a noise figure of 1.72 dB or less. While IP1dB is 10 dB, IIP3, the third-order intercept point, is as high as 4 db. The design only requires 7.4 mW of power. This multi-standard resistor less LNA design goes beyond.

#### 2.3 Key Challenges

Another significant trade-off in ROs is that the tuning range of an oscillator has a negative impact on the noise performance, as shown by a comparison between the tuning range and phase noise values in the table.

• The absolute value of phase noise reduces as the frequency tuning range widens.

A new parameter that is calculated using the absolute phase noise and the frequency bandwidth of the circuit is proposed in order to address this tradeoff.

- The sizes of the MOSFETs used in the various circuit components are specified.

- Because the ideal transistor sizing for the various topologies is not examined in this work, they are not all equally optimal.

- The uniform comparison uses the same sizing and produces oscillation.

## 3. DEMONSTRATING AND ANALYSIS

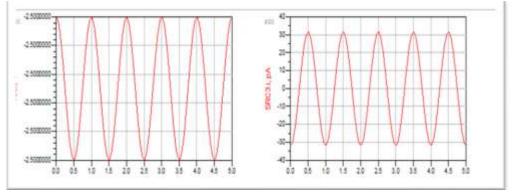

Only 14 MOS transistors are employed in the proposed system's two circuits, which have fewer parasitic characteristics and are therefore more suited for applications using RF ring oscillators. A current-mode RF link joins the two delay cells into a ring. It is realized that the quadrature ring oscillator is a two-phase, four-phase, and both of the current-mode RFQROs are made up of a phase-lag and a phase-lead delay cell. The simulated transient response during the delay cell's proposed current-mode RFQROThe simulated system is in its initial state, and the RFQRO begins approximately 300 ns later. Output signals are quadrature, with a transient response of 395 to 400 ns.

#### SOFTWARE REQUIREMENT:

The process of requirements analysis begins with the system requirement. It includes a list of the functional, performance, and security requirements for a certain software system. Additionally, usage scenarios from a user, operational, and administrative standpoint are provided in the requirements. A complete description of the software project, its parameters, and objectives is what the software requirements specification is there for. This outlines the project's user interface, hardware, and software requirements, as well as the intended audience. It outlines the client's, team's, and audience's perspectives on the project's functioning.

Engage the Database Administrator (DBA) in conversation as you write this section. All database management system (DBMS) files and non-DBMS files related to the system in development should be fully disclosed in this area. As needed for the specific project, further information may be added. Give a detailed data dictionary that includes information about each data element's name, type, length, source, validation guidelines, ability to create, read, update, and delete (CRUD), data stores, outputs, aliases, and description. Files for database management systems The following details, where appropriate (refer to the data dictionary), are included in this part, which exposes the final design of the DBMS files. A physical description of the DBMS schemas, sub-schemas, records, sets, tables, and storage; a refined logical model; normalized table layouts, entity relationship diagrams, and other logical design information;

## 4. RESULTS

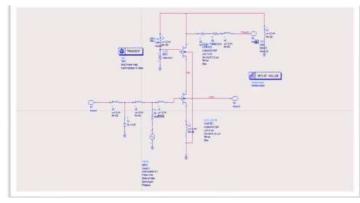

Figure 1 Switching of voltage to the Capacitors

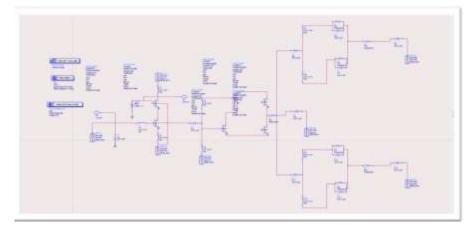

Figure 2 RF ring oscillators

Figure 3 Variation OF Voltage

ANALYSIS & DECISION

|                      |                       | MOSFET widths (nm)      |                       |

|----------------------|-----------------------|-------------------------|-----------------------|

| Circuit              | CMOS<br>inverter      | CS<br>transistors       | Bias<br>circuit       |

| Conventional<br>CSRO |                       | $W_n = 32$ $W_p = 64$   |                       |

| [12]                 |                       |                         |                       |

| [11]                 | W <sub>n</sub> =      | $W_n = 32$              | $W_n = 32$ $W_p = 64$ |

| PO1                  | 320                   | $W_p = 64$              |                       |

| PO2                  | W <sub>p</sub> =      | $W_n = 96$              |                       |

| PO3                  | 040                   | $W_p = 192$             |                       |

| PO4                  |                       | $W_n = 96$ $W_p = 192$  | 04                    |

| [10]                 | $W_n = 32$ $W_p = 64$ | $W_n = 320$ $W_p = 640$ |                       |

Table 1: MOSFET Dimensions For Different CSRO Architectures

| Architecture        | Power<br>(nW) | Maximum<br>Frequency<br>(MHz) | PDP<br>(fJ) | Tuning<br>Range<br>(MHz) | Phase Noise @<br>1MHz (dBc/Hz) | PNBP<br>(kdB) |

|---------------------|---------------|-------------------------------|-------------|--------------------------|--------------------------------|---------------|

| Conventional 167.30 |               | 38.68                         | 4.32        | 34.29                    | 78.71                          | 2.70          |

| [10]                | 167.50        | 340.24                        | 0.49        | 255.67                   | 73.23                          | 18.72         |

| 11] 230.20          |               | 157.06                        | 1.47        | 128.98                   | 71.39                          | 9.21          |

| [12]                | 169.06        | 43.48                         | 3.89        | 27.95                    | 78.92                          | 2.21          |

| PO1                 | 232.40        | 173.4                         | 1.34        | 136.86                   | 74.69                          | 10.22         |

| PO2 261.20          |               | 332.64                        | 0.79        | 276.50                   | 66.41                          | 18.36         |

| PO3 244.90          |               | 329.22                        | 0.74        | 262.29                   | 69.24                          | 18.16         |

| PO4                 | 181.80        | 170.78                        | 1.06        | 146.10                   | 75.76                          | 11.07         |

| Para                      | ameter       | Т    | VDD    | VTN   | VTP   | TOXN   | TOXP  |

|---------------------------|--------------|------|--------|-------|-------|--------|-------|

| Idea values               |              | 27°C | 0.5V   | 0.48V |       | 0.95nm | lnm   |

|                           |              |      |        |       | 0.43V |        |       |

| (%)                       | Conventional | 0.80 | 125.3  | 123.8 | 104.1 | 59.07  | 51.37 |

| uen (                     | [10]         |      | 112.5  | 93.1  | 85.8  | 46.59  | 45.05 |

| Frequency<br>Variation (% |              | 1.47 |        |       |       |        |       |

| Va Va                     | [11]         | 1.27 | 121.6  | 129.9 | 31.8  | 60.02  | 53.63 |

|                           | [12]         | 1.33 | 119.8  | 104.6 | 110.2 | 60.03  | 53.31 |

|                           | PO1          | 1.21 | 123.4  | 105.6 | 121.8 | 44.98  | 61.15 |

|                           | PO2          | 0.96 | 123.69 | 139.5 | 64.6  | 64.37  | 42.13 |

|                           | PO3          | 0.94 | 125.21 | 98.2  | 128.5 | 43.13  | 63.40 |

|                           | PO4          | 1.76 | 114.43 | 126.8 | 109.1 | 60.50  | 55.23 |

Table2: Effect of PVT variations On Oscillating Frequency

#### 5. Conclusion

This research looks into the potential of four new CSRO architectures. There are various CS delay stage topologies described in the literature. There are eight distinct circuits in all. When essential characteristics like maximum frequency, tuning range, and phase are contrasted power usage and noise. To take into account the compromises between these characteristics, various oscillators can be compared in light of two crucial the recently suggested PNBP and the well-known PDP characteristics. According to simulation results, the current CSRO architecture with the output switch approach delivers the best PDP and PNBP performance. However, PO3 and PO4 proposed CSRO designs offer nearly comparable performance in terms of PDP and PNBP with a significantly smaller transistor count (5 fewer transistors) smaller area need as a result..

#### Future Work

The output switch-based CSRO now in use has equivalent optimal PDP and PNBP outcomes to two recently proposed CSRO architectures using one NMOS sink or one PMOS source, according to simulation results.but with the benefit of a smaller area required. Additionally, all four proposed When contrasted, architectures perform better in terms of PDP and PNBP. to standard CSRO. The CSROs' performance is also tracked and compared in relation to Process-voltage-temperature (PVT) parameter changes. Then, the power consumption and frequency of each circuit are compared. Power delay product (PDP), bandwidth, maximum frequency, phase noise, and PNBP. Utilizing the 16 nm PTM High, simulations for three stage CSROs are performed. Technology model for performance (HP) in Cadence Virtuoso.

#### 7. References

- H. Yoon et al., "A 0.56\_2.92 GHz wideband and low phase noise quadrature LO-generator using a single LC-VCO for 2G\_4G multistandard cellular transceivers," IEEE J. Solid-State Circuits, vol. 51, no. 3, pp. 614\_625, Mar. 2016.

- H. Yoon, Y. Lee, J. J. Kim, and J. Choi, "A wideband dual-mode LC-VCO with a switchable gate-biased active core," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 61, no. 5, pp. 289\_293, May 2014

- B. Prameela, and A. E. Daniel. "Design of low noise amplifier for IEEE standard 802.11b using Cascode and modified Cascode Techniques," in Global Colloquium in Recent Advancement and Effectual Researches in Engineering Science and Technology, Elsevier, 2016, pp. 443– 449.

- 4. X. Fan, E. Sanchez Sinencio, and J. Silva Martinez. "A 3GHz-10GHz common gate ultrawideband low noise amplifier," Presented at the 48th Midwest Symposium on Circuits and Systems, Covington, KY, USA, August 7–10, 2005.

- 5. 5.C.-C. Chen, and Y.-C. Wang. "A 2.4/5.2/5.8GHz tripleband common-gate cascode CMOS low-noise amplifier", Circuits Systems Signal Processing, Springer, 2016.

- E. Kargaran, Y.Mafinejad, K.Mafinezhad, and H.Nabovati, "A new Gm-boosting current reuse folded cascode LNA," IEICE Electron. Express, Vol. 10, no. 24, pp. 1– 6, 2013.

- A. Andrew Roobert, and D. Gracia Nirmala Rani. "Design and analysis of 0.9 and 2.3GHz concurrent dual-band CMOS LNA for mobile communication", Int J Circuit Theory Appl, pp. 1–14, 2019.

- A.Hashim, N. M. Noh, S. K. KunhiMohd, Y. Mohd Yusof, M. Haidar Hamzah, M. Tafir bin Mustaffa, A. Abd Manaf, andO. Sidek, "A 0.13μmCMOS PCSNIM LNA formultistandard 0.9, 1.8, and 2.1GHz mobile application," IETE.