## International Journal of Research Publication and Reviews

Journal homepage: www.ijrpr.com ISSN 2582-7421

# **System on Chip Design Challenges**

## Savitha M M<sup>1</sup>, Devisetti Niranjan Kumar<sup>2</sup>

<sup>1</sup>Assistant Professor, Dept. of ECE, SJCIT, Chikkaballapur, India

## ABSTRACT

The SOC components and features with regard to future challenge. The diligent advancement inside the field of electronics and equipment, the machines or the contraptions are getting smaller and more successful in comparison with the more prepared machines or contraptions. Unusual challenges on the system on chip soc arrange courses of action have been risen since of the ceaseless headway of developments of semiconductors, soc gives a organize for the execution of different applications, and it'll make a transformation on the arrange of long run of contraptions systems, soc makes a difference in making the total system on a single chip and the chip will be uncommonly humbler in comparison with the total system. The soc has almost in reducing the space and the fetched of manufacturing. Underneath this commitment few crucial challenges have been centered additionally the unsolved issues concerned around the testability and arrange of soc had been centered on the development inside the field of electrical and hardware

Keywords--System-on-Chip(SOC), Gadgets Framework, ASIC, CMOS Technology.

#### I INTRODUCTION

The Hustle of Semiconductor advancement shapes and the intrigued for complex and exceptionally joined applications have incited the prerequisite for exceptionally successful plan techniques to bargain with the multifaceted nature of the structure and to fulfill time to-showcase limitations later on. The SIA direct predicts a thickness of 2 billion transistors for each chip for ASIC advancements and DRAMS a thickness of 48 GB for each Chip. The compromise thickness of 30-40 million transistors for each chip is available and this as of presently engages system-level on-chip coordination. Within the field of progressed structure, system-on-chip courses of action previously become state of-the-craftsmanship.

In some times due to size constraints it is not possible to integrated the RAM inside the system on chip. in such scenarios the memory package stack about the soc package there are connected using ball grid array. This kind of package arrange is also called as package-on-package arrangement. It reduces the cost and the size.

The SOCs are recognized by joining some prestructured centers on one and a comparative pass on. Routinely sections like processor centers committed ASIC squares, interfacing and memories are joined to frame equipment/programming courses of action. and execution prerequisites as for the whole framework to be consolidated.

## II METHODOLOGY

The reuse of parts, pointing for a course of livelihoods, might be a procedure to diminish the arrange exertion, which is remarkable from programming structure for a long time as of directly. Within the field of ASIC structure, the reuse of squares has been cleaned in setup houses for the foremost parcel inside the sort of movement of existing things. Since of shorter thing cycles and rapidly developing thing multifaceted nature, various orchestrate organizations will progressively more insinuate to module centers from outside. In the midst of the strategy of the exchange of course of action ruins from the essential supplier to the integrator authorized headway (IP) issues must be considered.

Fig: IP based arrange stream

<sup>&</sup>lt;sup>2</sup>Student, Dept. of ECE, SJCIT, Chikkaballapur, India

<sup>&</sup>lt;sup>1</sup>savithaa.hiremath@gmail.com, <sup>2</sup>niranjandevisetty@gmail.com

Fig. shows Appears systems an IP-based organize stream. The assurance of modern IPs is performed subordinate on demands rising with modern thing classes to be figured out. Amid the detail, the run of utilizations for the IP joining must be evaluated and the essential all-inclusive statement of the IP square to be made must be settled. In light of the IP detail, an IP show is grown (Delicate IP). Correct and well-organized documentation is crucial for future changes and updates of the square. The IP-model can clearly be appropriated as sensitive IP or it will be combined by the IP provider for a committed objective advancement bringing around a difficult IP. The apportionment of the IP can be performed authentically by the provider or by an IP library supplier. For the blend of an IP prevent into the client's thing arrangement, support organizations must be given. In this stream chart, a tight collaboration of IP providers, wholesalers, and the client is required to abuse the potential change of efficiency. Concerning the efficiency addition of IP-based structure, a couple of impediments of the strategy must be considered: re-ease of utilize of arrange sections makes an intrigued for agreement. Agreement routinely joins misplaced execution and extended space to be covered in-circuit test.

#### III TESTING OF SYSTEMON CHIP

The center based structure method, talked almost in section 2, has provoked extended plan benefit, it presents additional test-related issues, which are anticipated to, among others, licensed advancement security. These additional testing issues, beside the test issues actuated by the multifaceted nature and heterogeneous nature of SOC, show exceptional challenges to the SOC testing arrange. This section will conversation around many of these challenges. It ought to initially be taken note that, indeed in spite of the fact that the core-based structure strategy is like a standard system-on board SOB plan where person chips are arranged and a short time later joined into a board, creation trial of SOC which of Wail are diverse. In Cry testing, the person chips are manufactured and attempted to begin with some time recently they are facilitated into the board. The person SOC centers, whereas preplan and pre-verified, won't be attempted until they are facilitated into a framework chip. In this way, a center isn't attempted autonomously, but instep as a bit of the common framework chip test. This infers the parcel and-vanquish testing method generally utilized to oversee the capriciousness of testing an complex board can't be direct connected in SOC testing.

#### V BLOCK DIAGRAM

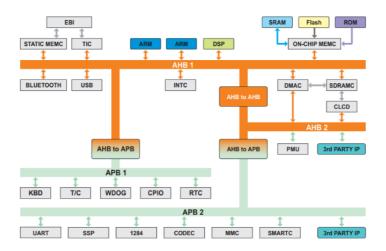

Fig: system on chip

Fig shows appears Framework on chip reliance that really characterizes an SoC engineering is the kind of processor that one employments as the central handling component. At Wipro, noteworthy center has been on the ARM processor innovation, since we accept that will drive the advancing showcase for embedded applications, versatile gadgets and following era data apparatuses. Our ability with ARM centers and innovation is additionally a subordinate of our longstanding affiliation with ARM, and our status as an endorsed ARM Plan Center. The SoC's target application requests may necessitate the inclusion of DSP centers within the plan thought. Another plan angle to be thought through is the kind of processor and framework Transport that's to be executed inside the system. The utilize of standard buses like AHB Progressed HighPerformance transport and APB Progressed peripheral transport is unquestionably invaluable vis-a-vis the utilize of restrictive buses. With standard buses, the integration assignment of putting together the SoC gets to be simpler, particularly in case the IP centers that are accessible bolster the chosen standard transport convention.

## VI DESIGN FOR TEST STRATEGY

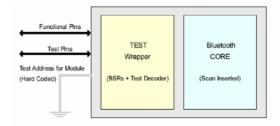

Fig: module level scan

Fig explains Module level filter confirmation shapes such a vital viewpoint of SoC plans, and since fabricating abandons are a no-compromise zone. SoC stream commands Plan for Test (DFT). In this technique, most common physical surrenders are demonstrated as flaws and vital circuits are included within the plan to encourage checking for these issues. These techniques and automated forms that insert logic in arrange to extend the plan testability shape the pith of DFT.

## VIIADVANTAGES

- SoC essentially has littler impression and space prerequisites since all the components are on the same chip and inside

connected

- A littler estimate implies it is lightweight.

- Higher execution and adaptability due to expanded sum of circuits on the chip.

- Application-specific SoCs can be cost-efficient

- More prominent framework unwavering quality and lower control requirements.

- SoC gives more prominent plan security at equipment and firmware levels

## VII APPLICATIONS

Speech-Signal-Processing:

Discourseacknowledgment (moreover called voice acknowledgment) centers on capturing the human voice as a advanced sound wave and changing over it into a computer-readable format.

• Information Communication -- This can be concerned with communication between computer frameworks or devices. SoC applications permit two sorts of information communication as said below: Wire line Communication: 10/100 Based-T, DSL, Gigabit Ethernet.

## VIII CONCLUSION

System-on-chip has been a indistinct term that mysteriously holds out a parcel of energy, and has been picking up force within the hardware industry. Whereas the potential is tremendous, the complexities are a few, and countering these to offer successful plans may be a genuine designing challenge. Mechanical progresses cruel that totalframeworks can presently be executed on a single chip. The benefits that this brings are critical in terms of speed, zone and control. The reasons are not distant to see: SoCs make accessible, on a single piece of silicon, the inserted IP and tall system-level integration required for execution requesting applications nowadays. This enables semiconductor producers to cost-effectively meet particular framework prerequisites while conveying competitive time-to-market advantage.

## **REFERNCES**

- [1] D Chin, V Linder and K Sia, Commercialization of microfluidic point-of-care diagnostic devices, International Research Journal of Modernization in Engineering Technology and science, Vol. 17, October 2018, pp. 99-106.

- [2] J Bonneau, A Miller, J Clark, A Narayanan and A Kroll, Research perspectives and challenges for bitcoin and cryptocurrencies, Institute of electrical and electronics engineering, vol. 14, November 2015, pp. 256-275.

- [3] P Guerrier and A Greiner, A Generic Architecture for on-Chip Packet-Switched Interconnections, Institute of electrical and electronics engineering, Vol. 10, April 2000, pp. 250-256.

- [4] S Kumar, A Network on Chip Architecture and Design Methodology, Journal of the International Measurement Confederation, Vol. 18, July 1996, pp. 177–183.

- [5] F Karim and S Dey, On-chip Communication Architecture for OS Network Processors, International Journal of Research of Scientific and Engineering Research, Vol. 18, June 2014, pp. 150-165.

- [6] J Liang, Single-Chip Communication Architecture, International Journal of Innovative Science and Research Technology, Vol. 12, May 2016, pp. 300-325.

- [7] S Peh and W Dally, A Delay Model for Router Micro-Architectures, International Conference on Smart Systems and Inventive Technology, Vol. 10, January 2014, pp. 200-206.

- [8] W J karan and B Towles, On-Chip Interconnection Networks, International Journal of Research of Scientific and Engineering Research, Vol.15, June 2018, pp. 123-136..