# **International Journal of Research Publication and Reviews**

Journal homepage: www.ijrpr.com ISSN 2582-7421

# ETHERNET PACKET GENERATORA PROTOTYPE

# P. Dheeraj Reddy, Y. Badrivishal, B. Premkumar

Email ID: 18699A0425@mits.ac.in, 18699A0409@mits.ac.in, 1960A0406@mits.ac.in,

#### ABSTRACT

In this paper, we use FPGA to model and implement the 802.11 Grouped Distributed Coordination. It is distributed random scheme based on the Carrier Sense Multiple Access with Collision Avoidance (CSMA/CA).DCF has mechanisms particularly, the primary access and the RTS/CTS get entry to mechanisms. Grouping of these DCF is known as GDCF. Due to this, the content in the medium is reduced which in-turn increases the throughput and the overall performance of the community.

In these a basic ethernet packet generator hardware prototype description in Verilog-HDL is developed, however for the actual data transmission Ethernet frame is encapsulated in an Ethernet packet ,only the packet generation process is given special attention. Basic frame format which is required for all MAC implementation is defined in **IEEE 802.3 standards**. The main objective of this project is to develop a custom hardware for a basic Ethernet packet generator. As the high speed process ability, FPGA is used.

### 1. INTRODUCTION

In present as the technology increases theuse of wireless communication is also increasing. These wireless communication plays a significant role in IEE 802.11 WLAN technology. And FPGA becomingone of the most important factor in wireless communication for its high reliability and high speed. It is mostly used for networking solutions and addressing standards of WiMAX and other WLAN technologies. For networks with multiple users, different users communicate with each other, thereby overlapping with each other leads in a collision. And good requirement of basic Ethernet packet generator needed. The objective of this paper is to develop basic Ethernet packet generator hardware prototype. The advantages are It creates abeautiful emulation environment that can simulate many simulation validation scenarios. You can use these methods to verify from the most complex hardware design to the simplest hardware design. Less traffic in the channel.

Packet Generator is a software tool that will be running on a Host PC and create traffic designs. Ethernet parcel generator is an item that creates series of Packets which can be utilized by emulator stage to produce traffic on DUTs interfaces. Additionally, it very well used on Simulation platform to generate traffic on simulation environmenton DUTs interface. Packet Generator permit us to make and send any possible packet or sequence of packet on Ethernet link.

There are five types of Ethernet frame:

- The Ethernet Version 2 or Ethernet II frame, the socalled DIX frame (named after DEC, Intel, and Xerox

- Raw 802.3 frame without LLC

- IEEE 802.x LLC frame

- IEEE 802.x LLC/SNAP

Wireless communication is widely usedbecause of its convenient mobility. TheIEEE802.11b standard includes two mainoperations: Distribution Coordination Functions (DCF) and Point Coordination Function (PCF). Using VHDL the CSMA/CA and the IEEE802.11b Physical and MAC are modeled in this paper. TheDCF is based on the CSMA/CA protocol. CSMA/CA does not detect a collision byhearing own transmission, thus a positiveacknowledgement is transmitted by the destination to indicate the successful Packet transmission.

Communication among various users in a network entails a collosion among them. These collosions among users leads in theloss of power and lack of time. For these a approach is used to clear up this difficulty called CSMA/CA is a MAC protocol in which node/station verifies the absence of traffic before transmitting onto a shared transmission medium. The station/node exams whether or not the medium is to be had for transmission that is if it idle . This is known as Carrier Sensing (CS). Each tool can bring or gather statistics from each different tool in a community. This is known as MultipleAccess(MA). Once the packet which is to be sent is received by the station, itchecks whether the station is idle or no. If it is idle, the packet gets transferred across the channel else it waits till the medium is free

Making communication more efficient & reduction in energy consumption in wireless network is an main issue to be taken into consideration in the layout of MAC protocol When a large number of nodes share a wireless channel for data transmission, and the user is intermittent work, the requirement to use the MAC protocol in the random multiple access technology (DCF). In these a design of MAC protocol supported FPGA is proposed, that uses the Verilog –HDL.

It uses a random multiple access technology, if a node wants to send data, first to capture the channel, after the achievement of data frameto send; on the equal time each node can pay attention to the status of the line, the road is conflicting or busy, each node adjusts the data transmission time, so reduces the simultaneity in the channel, improves the channel utilization rate.

Most of existing researchers used simulation and analysis methods to study WLAN. In this paper, we tend to use FPGA to model and implement the 802.11 Distributed Coordination perform (DCF). Firstly, we outline the practical blocks and theiroperating behavior; then, we describe the corresponding implementation onto FPGA devices. the planning of all pratical blocks strictly follows the specifications of the 802.11 standard.

In this way, the proposed FPGA-based DCFmodule can flawlessly interconnect with existing business WLAN chipsets; moreover allboundaries of the 802.11 DCF are totally open to framework architects (i.e., can be handily arranged/changed). The proposed execution provides a normative prototype by which the development of DCF based systems can betested and evaluated conveniently.

In the current Medical Linear Accelerator (LINAC) systems with Field Programmable Gate Array (FPGA) based control console, the greater part of the subsystems of the LINAC were controlledand checked utilizing sequential specialized techniques like RS-232, RS-422 or RS-485. Presently a days, the greater part of the subsystems or regulators utilized in theLINAC system support Ethernetcommunication which has not been carried out in the system at this point. The conventional sequential specialized strategiesas referenced above additionally have a limit of data transfer speed. This paper will work with interoperability between different subsystems of the LINAC associated utilizing the Ethernet protocol. This system is designed in ARTY-7 FPGA and has been executed using VHDL language.

The objective of this paper is to develop basic Ethernet packet generator hardware prototype. It creates a beautiful emulation environment that can simulate many simulation validation scenarios. Youcan use these methods to verify from the most complex hardware design to the simplest hardware design, Less traffic in the channel.

#### Ethernet:

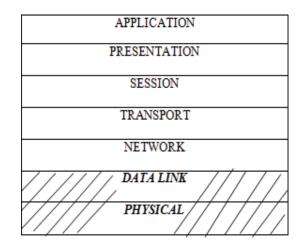

Ethernet is a family of computer networkingtechnologies commonly used in local area networks (LAN), Metropolitan area networks(MAN) and Wide area Networks (WAN). It supports higher bit rates and longer link distances. Ethernet sometimes means TCP/IP protocol. Ethernet only defines the data link and physical layers of the Open Systems Interconnect (OSI) reference model whereas TCP/IP defines the transport and networklayers respectively of the same model. TheEthernet generally defines the lower two bytes of the OSI reference model as shown belowfigure.

Fig 4.1. Ethernet defines the lower two layers of the OSIreference Model

For this software design we develop a basic Ethernet packet generator hardware prototype in Xilinx. Prototyping means building an actual circuit to a theoretical design to verify that it works, and to provide a physical platform for debugging it if it does not. The vivado Design Suite is a software suite created by Xilinx for the synthesis and analysis of Hardware Description Language.

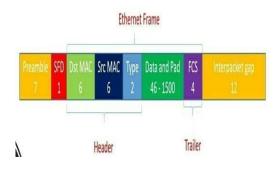

## 2. STRUCTURE OF ETHERNET FRAME

#### Fig.4.2: structure of Ethernet frame

**Preamble** is a stream of bits used to allow the transmitter and receiver to synchronize their communication. **Start Frame Delimeter(SFD)** is always 10101011 and is used to indicate the beginning of the frame information. **Destination MAC** is the MAC address of the machine receiving the data. **Source MAC** is the MAC address of themachine transmitting the data.**Data/Padding** The data is inserted here. This is the place where the data and IP header is put on that you are running IP over Ethernet. This field contains IPX information if you are running IPX/SPX (Novell). Contained within the data/padding section of an IEEE 803.2 frame are four specific fields: DSAP, SSAP, CTRL, NLI. **Length** This is the length of the whole Ethernet outline in bytes. **Frame Check Sequence** This field contains the FCS which is calculated using a CRC. It allows Ethernet to detect errors in the Ethernet frame

### 3. SYSTEM IMPLEMENTATION

Consider a pc and a server, before sending an Ethernet frame, PC sends a Preamble signal which is a series of 7 bytes pattern of alternating 1 and 0 bits.

The preamble signal plays two roles

- It notify the FTP server determine that PC is going to send an Ethernet frame to FTP server.

- It makes the FTP server determine how much time it takes for each bit to go from PC to the FTP server. From there, the FTP server synchronizes its clock with the PC.

- And after receiving 7 bytes of preamble signal, the FTP server expects to receive the (SFD).

- The SFD is the eight bit value of 10101011 that makes the end of the preamble, and shows the starting of the Ethernet frame.

- The SFD signifies the fields that follows are:-

- The bytes destination MAC address detects the intended recipient of this frame.

- The 6 bytes source MAC address detects the sender of this frame.

- The type fields identify the type of network layer packet that sits inside the Ethernet frame.

- The most common network layer protocols are both from TCP/IP:IPversion 4 (IPV4) and IP version 6(IPV6)

- Frame check sequence (FCS)defines a way for nodes to find out whether a frame's bits changed while crossing over an Ethernet link. It works as below :

- The sender applies a complexity math formula to the frame before sending it, then stores the result of the formula in the FCS field.

- Then, the receiver applies the same math formula to the received frame.

- The receiver then compares its own result with the sender's results. If the results are the same, the frame will not change

# 4. OUTPUTGRAPH:

| Name Value                | L,000 ma | 1.500 ns                   | 2,000 ms | \$.400 no | D. 000 84 | p. 500 Ks | 14,000 R.4       | 4,500 NF | [\$,000 ns | 15, 500 na | e.000 ma | 16,500 N# | 17,000 84 | р. 500 км   | 18.000 KK | 19,500 He | 19,000 ma | 87 |

|---------------------------|----------|----------------------------|----------|-----------|-----------|-----------|------------------|----------|------------|------------|----------|-----------|-----------|-------------|-----------|-----------|-----------|----|

| e padet 1<br>e pade. Id D |          | <u>Preamble</u><br>8 bytes | Dest.    | Source    | ↔ Len     | gth (2 b  | nurun.<br>bytes) | تستوتية  | Da         | :a (64 b   |          |           |           | <b>n</b> nn |           | CS        |           |    |

|                           |          | y.                         | •        | 6 bytes   | 51 - 751  |           |                  | Ethern   | et Fran    | ne         |          |           |           |             | by        | 4<br>tes  |           |    |

|                           |          |                            |          |           |           |           |                  | Ethern   | ctifui     |            |          |           |           |             |           | *         |           |    |

## 5. RESULT

From above, we can see all frames can co-exist on the same link. Maximum frame length from the starting of the Ethernet frame i.e., from the destination MAC to the data MAC both inclusively of 6 bytes each. And the minimum frame length of 2 bytes is allowed for thesame fields.

The Data/ Padding come with the length of 64 bytes. Preamble is of 8 bytes and the trailer part that is Frame Check Sequence(FCS) has the length of 4 bytes defines a way for nodes to find out whether a frame's bits changed whilecrossing over an Ethernet link

### 6. CONCLUSION

In this paper, we have introduced a straightforward model to create a block design environment which included with few inbuilt Xilinx IPs namely, FIFO generator and utility vector logic.

We have seen the implementation and result of the Ethernet frame structure with respective of bytes. Therefore our project shows the development of a basic Ethernet packet generator hardware prototype description on FPGA(Field Programmable gate array) by using the Verilog-HDL programming language.

### REFERENCES

- HemaManjule, SavithaUpadhya, NilashreeWankhede, ManojKumbhare,Kiran Thakur, R.Krishnan, "Ethernet Implementation on FPGA", 2020 International Conference for Emerging Technology(INCET), DOI:10.1109/INCET49848.2020.91 5404 6.

- [2] JieWu ,Jie Zhang, Zhao Han , Liefeng Liu and Juan Dong ,"The Implementation of a High Speed Ethernet Traffic Generator Based on FPGA". University of Science and Technology of China, Hefei, 230026

- [3] IEEE Computer Society. IEEE Standard 802. 11: wireless LAN medium access control (MAC) and physical layer specifications, 2003.

- [4] IshaTamrakar, C. M. Ananda, Pradeep Kumar B and P SreeRamani, "Design and Implementation of Ethernet based analyzer for avionics serial bus on FPGA", IEEE International Conference on Recent Trends in Electronics Information Communication Technology, May 20-21, 2016.

- [5] Mrs. Santhameena.S, Aninika S Adappa,K.DhirajKumar,Ananya Boyapati,dept.of ECE PES University Bangalore, India. "Implementation of unslotted and slotted CSMA/CA for 802.11 and 802.15.4 protocol", 2019 Global Conference for advancement in Technology,(GCAT),DOI: 10.1109/GCAT47503.2019.8978 395.

- [6] Yang Jundon, XuZhi, BaoLiyong, HeMin, Wang Kun, ZhouShaojing, "A Design of MAC Layer DCF Protocol for IEEE 802.11 Network Based on FPGA", 2017 International Conference on computer systems, Electronics and Control (ICCSEC). DOI: 10.1109/ICCSEC.2017.8446891