# **International Journal of Research Publication and Reviews**

Journal homepage: www.ijrpr.com ISSN 2582-7421

# Analysis and Comparison of Various CMOS Leakage Power Reduction Techniques

# M Venkata Sandeep Reddy, G Vamsi Krishna, C Veera Raghava, R Kiran Kumar

Department of Electronics and Communication Engineering, Madanapalle Institute of Technology & Science, Madanapalle, Andhra Pradesh, India

# Corresponding Author: kirankumarr@mits.ac.in

# ABSTRACT

Leakage power has turned into a genuine worry in nanometer CMOS advances. Before, the unique power has overwhelmed the all-out power dissemination of CMOS gadgets. Notwithstanding, with the constant pattern of innovation scaling, leakage power is turning into a principal supporter of power utilization. In the past numerous strategies had been proposed for leakage power decrease like constrained stack, languid stack, sluggish manager, double rest approach and so on utilizing methods like semiconductor measuring, multi-Vth, double Vth, stacking semiconductors and so on. In nanometer innovation power has turned into the significant issue in light of the fact that rising semiconductor count, higher speed of activity, more prominent leakage flows. Power dispersal is relative to speed of activity. For power the executive's leakage power likewise assumes a significant part in low power VLSI plans. Leakage power increments at a quicker rate than dynamic power in innovation age. In this paper, new strategies have been proposed for the leakage power decrease in 90nm innovation. The proposed strategies will be contrasted, and the past existing leakage decrease procedures and furthermore depicts about the different power scattering techniques alongside leakage power the executive's methods for low power VLSI circuits and frameworks. The outcome is mimicked utilizing Microwind 3.1 in 90nm CMOS innovation at room temperature.

# INTRODUCTION

The technique of building an integrated circuit (IC) by merging thousands of transistors into a single chip is known as very-scale-scale integration (VLSI). With the advancement of semiconductor and communication technologies in the 1970s, VLSI was born. A VLSI device is used as the microprocessor. VLSI is a type of integrated circuit that has several devices on a single chip. The word, like many other scale integration classifications based on the number of gates or transistors per IC, dates back to the 1970s. The progressions in enormous scope joining advances are primarily answerable for the hardware business' uncommon development. The quantity of choices for ICs in control applications, broadcast communications, superior execution registering, and customer hardware.

Power utilization is a significant thought in the plan of Very Large-Scale Integration (VLSI) circuits, which utilize the Complementary Metal Oxide Semiconductor (CMOS) as the major innovation. The ongoing spotlight on low power isn't only because of the new ascent in portable application needs. Power utilization has forever been a significant issue, even before the portable age. Numerous analysts have introduced numerous strategies to defeat the power dispersal issue, going from the gadget level to the compositional level and then some. In any case, since there is no uniform answer for wipe out tradeoffs between power, dormancy, and region, fashioners should pick OK ways to deal with meet application and item prerequisites.

CMOS power utilization is comprised of both dynamic and static parts. At the point when semiconductors switch, dynamic power is consumed, and static power is consumed paying little mind to semiconductor flipping. Since dynamic power represented 90% or a greater amount of all out-chip power (at 0.18 innovation or more), it was generally the absolute most significant concern for low-power chip planners. Therefore, a few recently proposed approaches zeroed in on unique power decrease, for example, voltage and recurrence scaling. Static power has turned into a central issue for existing and future innovation as component sizes diminish, for instance, to 0.09 and 0.065. Kim et al. show that subthreshold spillage power scattering of a chip might outperform dynamic power dissemination at the chip level, in light of the International Technology Roadmap for Semiconductors (ITRS).

Expanded subthreshold spillage power is one of the essential drivers of spillage power development. At the point when the size of a specialized component is decreased, the stock voltage and edge voltage are diminished too. As edge 1 voltage brings down, subthreshold spillage power develops dramatically. Moreover, the short channel gadget's development diminishes the edge voltage considerably further. Entryway oxide spillage power, brought about by the burrowing current by means of the door oxide separator, adds to spillage power notwithstanding subthreshold spillage. Since entryway oxide thickness will drop as innovation propels, door oxide spillage power in nanoscale innovation might be identical to subthreshold spillage power on the off chance that not controlled suitably. Notwithstanding, we expect that elective methodologies will be utilized to settle entryway oxide spillage, for example, high-k dielectric door encasings.

The circuit designer used to draw the schematic and maybe add some annotations or notes for the layout designer, then throw the schematic over the wall. The layout designer went across the wall to the circuit designer after reading the notes and making some placements and routing. Finally, the

circuit designer would check for symmetry and matching in the IC layout and request revisions, establishing a loop that had to run until the matching requirements were fulfilled.

Simple plan with regards to coordinated circuit (IC) plan is a discipline that spotlights on the production of circuits that work in and are improved for ceaseless time-space conduct. Normal targets of simple plan include:

- Signal fidelity

- Amplification

- Filtering

Simple plan is the foundation for all IC plan since every one of the principal gadgets in an IC answer a constant time boost. Many plan issues are introduced by current IC innovation. The creation strategy for high innovation hubs has a great deal of variety. Inconstancy is likewise brought about by the genuine situation of countless gadgets on current ICs. Changeability in functional voltage, working temperature, and execution are indications of this fluctuation. Signal twists can be brought about by thickly stuffed gadgets communicating with another, as well as the silicon substrate, bundle, and board. These impacts can occur across gadgets as well as inside a solitary incorporated circuit.

Most people think of complicated microprocessor architecture when they hear the term "integrated circuit design." Digital design approaches are used to create these circuits, which focus on the propagation of discrete values, or "ones and zeros." It's crucial to realise that this paradigm of propagating "ones and zeros" is employed to make large network analysis easier. Because the actual components in every circuit respond to a constantly changing stimuli, analogue circuit design is the cornerstone of digital circuit design.All of these impacts must be compensated for in analogue design to maintain three fundamental qualities: fidelity/precision, consistency, and performance. Some of the activities used to model and reduce these impacts include reliability analysis and signal integrity analysis.

# **POWER REDUCTION TECHNIQUES**

Digital circuits reduce photoelectric maneuver flux accepting conventional forms considered switches. The advent of the vacuum tube produced radio production to a tremendous impact, but suffered from some pitfalls, such as over-talent and large-group anode duty. The lie of electronic devices was a new effect, including personally calculating part production, which fascinated several watts of capacity. This was a treasure trove for reduced volume maneuvers. The combination of many functions in a unique chip and the superiority in the execution of the circuits has exceeded the reduction of the amount of features and has grown in the capacity Cancer in all areas, which is a necessity in decent series. heat removal and discouraging composition. Low volume is a basic bureaucracy in the VLSI rule in a nutshell. The three strongest drivers of rapidly anticipated progress are space, competence and efficiency. In the past, reliability, cost, and disclosure were probably overkill, and the capacity reduction was insufficient. After different advances in ammunition promotion, complex active form such as PC, wearable maneuvers, portable phones, implantable therapeutic devices, the interconnected use of various news, concave capacity utilization and the associated use of trivial tools that require quick estimation, the requirement for weak volume has emerged. The high capability pattern infuriates numerous silicon failures that cause excessive heat. At 10°C the rate of rise heat component heat loss doubles. Some of the key design issues in VLSI production are impact cost, distance, pressure, ammo quantity, parts, heat drop and order wrapping as a result of hot and strong limits. The use of extreme competence is a decisive factor in absorbing more useful sounds, a pleasant, cohesive performer on a unique chip. With lower capacity abandonment, less heat is designed in the range, lower capacity utilization and lower need for heat destruction provisions, and accordingly extensive weathering concession is forged. Low competency approaches are distinctive in demand. The purpose of the data processing machine is that innovations accompanied by ammunition such as container phones, laptops increase battery development, amortize pressure and reduce the cost of hateful winding. Plastic bund les are used in circuits after the 1-2W capacity level. The purpose of the ammunition is to increase the layout like tablets and laptops, reducing the ignorance bias to half of the total ability usage. For reinforced, non-ammunition plans, it is a goal to achieve the reduced capacity that is lost after stabilization support. The occurrence of digitally connected circuits is discussed with the use of divine type. The combination of more exaggerated alarm rates, better active coupling, and smaller process geometries was delivered to the mainstream mass of ignorance. Scaling increases the size and depiction of photoelectric designs on a chip. Scaling helps increase the speed and repeatability of the flow and therefore important processing. As voltages scale physically lower that accompanies geometries, initial voltages must be reduced repeatedly to reap the success advantages of the new science, but the output current increases exponentially. Thinner rod oxides led to an increase in the opening of the efflux stream. Today outflow capability has developed a more fundamental problem in vendor connections and computer software for basic operations design. The main component of the flow is discharge with exponentially increasing backup -on current following decreasing design intervals, providing an infinitely increasing accord with core killer capacity utilization. In 65 nm and below sciences, discharge gives reason for 30-40% of vendor competence. According to the International Technology Roadmap for Semiconductors (ITRS), the possibility of accepting discharge volume pleasure still manages overall volume consumption as wisdom feature sizes backfire. While different process capabilities and path - level resolutions are capable of disrupting the flow in processors, at this place paper various new approaches are thrown to threaten the two together discharge and core capability following the minimum possible trade-off of space and delay. Modern digital circuits consist of the sense stick. Synthetic products have reached the evolving group of connectors of semiconductor (CMOS) electronics. Power usage has two parts: Dynamic Power and Leakage competence [2]. Live talent is only drunk when the edge functions and the signals change. Leakage or calm volume is constantly swallowed, even if the limit is useless. It is excessive and the individual wants to eliminate it [3]. Now the styles of scaling and volume reduction in transistors will cause sub - threshold currents to adorn a larger important component of the overall capacitance game. Leakage adequacy mainly depends on the increasing sub-threshold discharge current following the decrease in source capacity. To make the discharge volume modest, nice, harmonious performer judge, multi-Vth, dualVth, best replacement recommendation course draft, stacking transistors, two-fold Vdd, etc. Different tools with useful sounds that were discarded.

## **Power Distribution Factors**

In CMOS, there is volume utilization of streaming capability and live capability. Dynamic capacity includes trade competence and prevention capacity together. Switching ability is devoured when transistors are inactive, and bulk is avoided when a network of seduction and undercut moves nicely and off. Discharge capability for 0.18u and above is limited by live proficiency, but flow proficiency of 0.13u and below is essential. The dynamic volume loss is equivalent to the square of the supply substance. In deep submicron operations, the supply voltages and pickup voltages for MOS transistors

fatigue significantly. This reduces the base volume debauchery to some extent [4]. Static proficiency fun is proficiency amused because of currents flowing through a photoelectric design where no interference is made, and electronic devices are in an uninterrupted state. The leakage volume depends on the neutral distance and width of the group of chemical elements. It changes exponentially according to the origin power and additional limits. The reduction of supply voltages and gap voltages, which helps to lower the vital capability enjoyment for MOS transistors, reinforces the downside here. The subthreshold discharge current increases exponentially with increasing residual volume loss. The discharge current of a photoelectric maneuver is usually the result of reverse incomplete PN junction flow and Sub-source discharge.

Compared to sub-threshold flow, the discharge of reverse biased PN junctions is likely to be overlooked. Sub-threshold arc or sub-threshold flow or sub-threshold discharge current is the current that flows between the source and discharge of a MOSFET, in the sub-threshold rule or inactive exchange area, i.e., to recommend photoelectric devices for entry into the chamber. starting voltages under the tripping task. II. Disappearing Power Sources Power gratification is the amount of competence, that is, convinced of warmth and constantly immersed in powerful plans. The measurement of lost capacity is in watts. The three main sources of capability loss at the CMOS boundary are Stray current: Occurs when acknowledgment(s) and output(s) are generated, i.e., unchanged. Short -circuit current: Occurs when a CMOS innovation's N-MOS and P-MOS assume that current flows directly from the origin to ground. Logic changes: The nodes in a digital CMOS shift oscillate half-way through two information levels (0 and 1) that load and discharge capacitance in the correct series.

This burdensome and discharge causes Current to flow through the channel resistors of photoelectric devices, and the fun of capacitance marvels enters the written texts of past events. Leakage current and changes in principle, which fall under the category of quiescent capacity abandonment at the start of the leakage current, are classified under live capacity abandonment. The leakage current is caused by fake televisions with revers e bias current and sub-threshold current in parasitic diodes. In MOS transistors, the regulation of the reverse bias current occurs in the middle of the two-point discharge, origin and size rule, while the sub-threshold current is due to the variation load that exists in the tripping power below the origin temperature. If the feature size is 1 micrometer, the diode output of 1 unhealthy clutter is involved in the consumption behavior.

If a dc route is created in the middle of the supply rails and is grounded through advice and result exchange before the opening current takes place. Short-circuit current is as worrisome as bragging bar current. For an inverter output, the brag bar current is equivalent to the inverter port gain, twelve inches/30.48 centimeters calculated capacity, lower threshold capacity, repeat start, and signal rise/fall field and supply potential. In action changes, capacitive loads are loaded and completed and accordingly, competence creates arbitrariness. In the absence of load, maximum leakage from the hole current occurs and decreases as the load is created. Short-circuit competency usage is less than 15% of live talent usage, if the recommendation(s) and brand(s) are equivalent to the change occasion. The use of appropriate cycle and plan drawing methods can attempt to prevent and maintain the flow of flow. However, burdensome and unloading the load capacity dominates the capacity utilization and is probably equal to

#### Low Power Design field

Low capability that can threaten the person from the following determinants: 1. Voltage: One of the best choice schemes for volume reduction in circuits. The voltage and capacitance connection are chosen by the equation P = V2. If R V gets smaller, the capacitance is still ignored. Now consider V as V before observing the quadruple capacitance drop of individual 2. Its influence is borderline ubiquitous. Designers often sacrifice the material capacitance and file treatment produced for lower heat. This design range although the speed and latency fed are lower as Vdd gets closer to Vt. Physical capacity: Dynamic loss of competence in trading material capacitance is insufficient. Determining material capacitance before demolition and planning is a difficult task. It is therefore excessive to get full inside information on the establishment, conquest and plan accuracy of capacity theory. With lower travel, smaller wires, and smaller designs, the capacitance will likely shorten. The main reason when planning a conversion is interconnect capacitance is hassle - free according to the topography scheme. Data on enrollment bestowal, ancestors of superior subordinate functions, and incorporation and forging aid threatens relevant capacity. 3. Reasonable changes: Reasonable changes or changes in business influence active entertainment. With a lack of flexible business capacity, the disappearance is not the most important factor in many skills. The rational change eliminates the trade in two ingredients which means announcing fclkand E (sw). Fclk estimates the average end of volume return while E (sw) concludes the change number for each transfer product.

#### **Power Reduction Arrangement**

i) Reducing chip and power component formats to some extent SOI (Silicon Protector) with incomplete or fully utilized resources or by measuring a small CMOS content scheme. It is a straightforward but expensive method

ii) Advanced affects substrates such as multi chip piece MCM. It is a very smart but very expensive process.

iii) Potential Weight: Requires new structure and support circuits up to DC / DC conversion level and potential concave level converters. It is a low-level system but controlling the signal to transmit interference is important.

iv) Best Design: Investing in skills reduction by attracting a better design system is more limited and more powerful.

v) Appropriate skills for presidential programs. The completion of the EDA facilitates harvesting skills as well as the work being 71% 65% 54% 57% 51% 38/40 done. The four levels of absorption are the degree of relation of common sense, the degree of composition, the degree of composition and the level of the boundary. This is achieved by a high degree of variety of simulations.

System level: At all design levels, incoming input modules are detestable

**Sensible joining**: This level of absence is equal to the distance from the point of transmission of two points and the area of the network in the room. Various methods are used to replicate and add an RTL book based on the purpose of the exercise goal, the model delay and the objective activities. After the level of management, basic exercise and integration with analysis options are built on the ability to exchange flexible principles.

Visual design level: It equates between two points of netlist traffic and a chart based on the appropriate design of the radio, multiple VCRs and objective functions. Most tumor electronics are used for isolation, location, enlargement and line shooting. Under no circumstances the delay in exit trade takes time and work map to reduce capacity and reduce the burden on the trading port by proper listing, barrier establishment, department size increase and fiber. 3.4 Regional-level design: These adiabatic acceleration accommodations alternate with concave volume. Some applications are an unresolved configuration ring and are set up by an incomplete transmission of compressed volumes of electricity. DC / DC level converters and direct power level converters are inevitable in reducing the strike design capacity.

#### **Power Management Strategies**

Power president projects play an important role in the potential threat to digital entertainment. Some of the features of the game are deliberately created in this local paper the diminished knowledge of various sources, the current community of alarms, the variety of feed feeds, the community capacity in which it occurs, the body mass index and the substrate bias.

**Multi voltage**: Threshold service is a major indicator of power threats. This command helps to combine both important threats and power outages. The mixed use of the open style used in the same way is achieved. In terms of output the rate of decline of the service of greater opportunities than profit. During the active waking phase, the volume of the compressed spring is used to determine the concave volume according to the soup. As the gap temperature rises, the subthreshold current begins to come as a result of an increase in confused reproductive delays from the area. So great with a small fee for speed and field. This is a very useful design for reducing volume error.

**Multi-supply equipment**: In this system of erudition low-voltage supply and over-supply function equally introduces the fashion of movement. Nonessential processes are used in conjunction with reduced product volume and better physical delivery capacity used for error detection studies. The high heat offered following a disturbing practice helps to achieve a certain performance while the low material given in the unrestricted lessons helps to complete the work of low volume entertainment. Each level on the chip is destroyed into multiple grids. In these large and low power grids are shown as false in the operating flow. Many of the features available are used in analytical signal processors. It helps to control backwardness in the error detection study. Other known difficulties are the need for classification, subdivision and difficulty of assessment.

**Power transition**: According to the people who are present at the events the artist who helps most of the sleep is raised in the middle of the venue from two places and is actually low when the situation is disgusting by sleeping because it bothers him out. This form sets the output volume without any dramatic action. The two types of volume community present in event construction are fine grinding and raw grain. The design of the design additionally belongs to the people of the clock present in the way it happens. The misfortune associated with this work has been raised and delayed. The impact of better skills is the benefit associated with this approach.

**Body bias**: Body bias reduces the ability to relax by decorating the opportunity to create the capacity of individual electrical appliances associated with reduced water flow. The two most widely used patterns are Swapped bulk bias and the MOS bias strategy which is an important source. In SBB the distribution delay is short. This system make use of determine slight penalty on delay and field. RFID, biomedical mechanisms and sensor networks are few models where dead body biasing is active.

**Dynamic voltage and frequency**: Most occasionally used capacity presidency plan. In this design alarm commonness is belittled produce a decline in supply volume. It has the ability to humble capacity eating up of CMOS IC energetic guess and laptops. P = cfv2 + Pstatic (3) Voltage necessary depends upon the repetitiveness at that it is remark and accordingly if recurrence is beaten before create capacity maybe belittled. By this system 34% of competency is preserved. The decline insufficiency increases speed, correspondingly a largest benefit having to do with this means. It again offers augment. It is occupied for microprocessors, linked use of various radio connects scheme and cannons provoke photoelectric designs. 6.6 Clock crowd present at occurrence: This procedure reduces alarm signal occurrence in trading ability reduction of change. As feature force had demur timer recurrence of IC has nurtured so volume use takes place. Power vanishing is capital because alarm net as it has more important changing exercise. In alarm population present at occurrence design watch is blocked mobile of the circuits.

# RESULTS

The proposed Symatic design is successfully implemented in DSCH tool

### Symatic Diagram

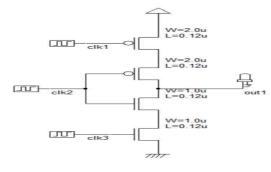

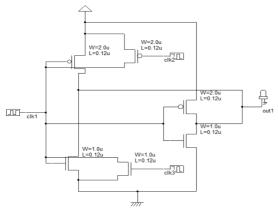

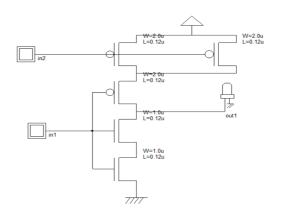

Figure 1: Sleep Transistor

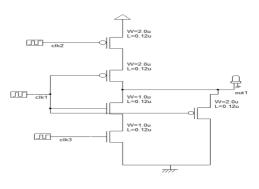

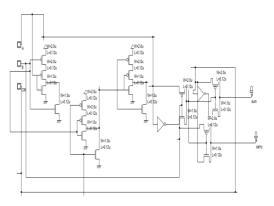

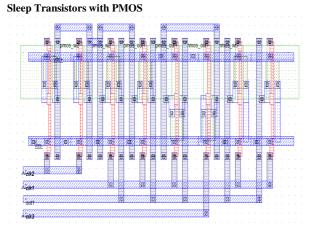

Figure 2: Sleep Transistor With PMOS

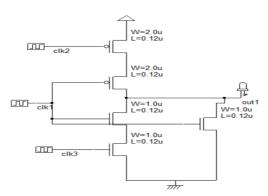

Figure 3: Sleep Transistor with NMOS

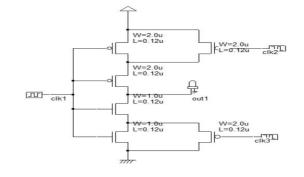

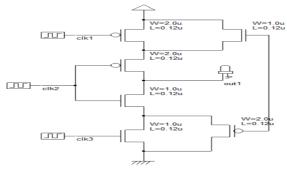

Figure 4: Sleepy Stack

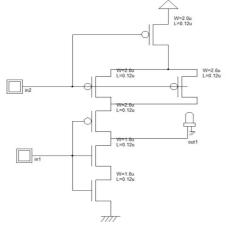

Figure 5: Sleepy Keeper

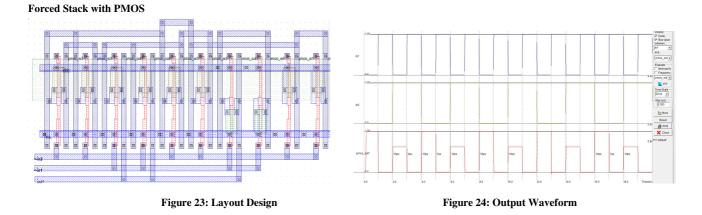

Figure 7: Forced Stack with PMOS

Figure 9: Variable Body Biasing with Bypass

Figure 8: Forced Stack with NMOS

Figure 10: Full Adder Using Stack

The proposed design is successfully implemented in MICROWIND tool

## Simulation Layout and Waveform

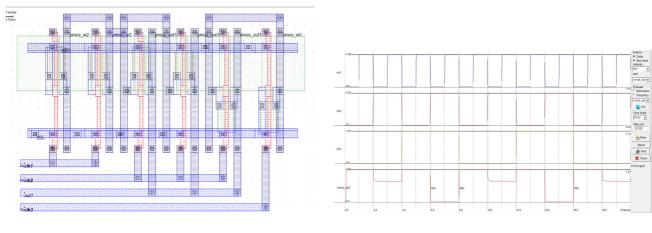

## **Sleep Transistors**

Figure 11: Layout Design

Figure 12: Output Waveform

Figure 11 represents the layout design of sleep transistor and figure 12 represents the output simulation waveform of the sleep transistor, here total power consumed by the sleep transistor is given by 0.  $757\mu$ w.For constructing sleep transistor we required 4 transistors, average clock to q delay is given by 7ps and finally the power delay product of sleep transistor is given by 5.299aJ.

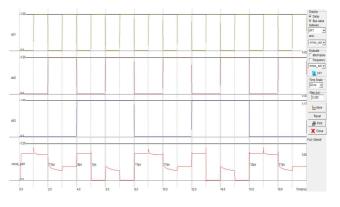

Figure 14: Output Waveform

Figure 13 represents the layout design of sleep transistor with pmos and figure 14 represents the output simulation waveform of the sleep transistor with pmos, here total power consumed by the sleep transistor with pmos is given by  $0.783\mu$ w.For constructing sleep transistor with pmos we required 5 transistors, average clock to q delay is given by 15ps and finally the power delay product of sleep transistor with pmos is given by 11.745aJ.

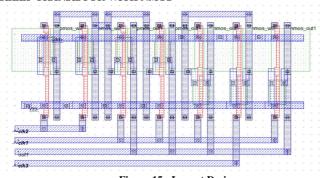

Figure 15 : Layout Design

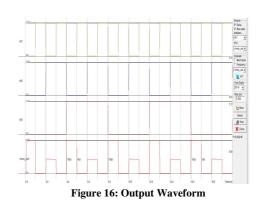

# SLEEP TRANSISTOR WITH NMOS

Figure 15 represents the layout design of sleep transistor with nmos and figure 16 represents the output simulation waveform of the sleep transistor with nmos, here total power consumed by the sleep transistor with nmos is given by 0.  $757\mu$ w.For constructing sleep transistor with pmos we required 5 transistors, average clock to q delay is given by 7.5ps and finally the power delay product of sleep transistor with pmos is given by 5.6755aJ.

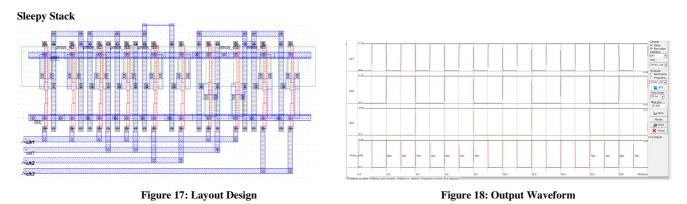

Figure 17 represents the layout design of sleep stack and figure 18 represents the output simulation waveform of the sleep stack, here total power consumed by the sleep stack is given by 2. 274µw.For constructing sleep stack we required 6 transistors, average clock to q delay is given by 7ps and finally the power delay product of sleep stack is given by 15.918aJ.

#### Figure 19: Layout Design

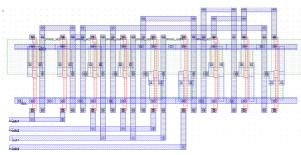

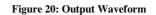

Figure 19 represents the layout design of sleep keeper and figure 20 represents the output simulation waveform of the sleep keeper, here total power consumed by the sleep keeper is given by 0. 980µw.For constructing sleep keeper we required 6 transistors, average clock to q delay is given by 10.5ps and finally the power delay product of sleep keeper is given by 10.29aJ.

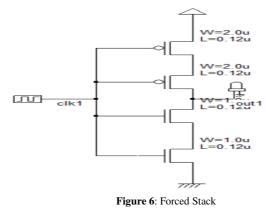

#### **Forced Stack**

Figure 21: Layout Design

Figure 22: Output Waveform

Figure 21represents the layout design of forced stack and figure 22 represents the output simulation waveform of the forced stack, here total power consumed by the forced stack is given by 2.694µw.For constructing forced stack we required 4 transistors, average clock to q delay is given by 7.5ps and finally the power delay product of forced stack is given by 20.25aJ.

Figure 23 represents the layout design of forced stack with pmos and figure 24 represents the output simulation waveform of the forced stack with pmos, here total power consumed by the forced stack with pmos is given by 3.  $794\mu$ w.For constructing forced stack with pmos we required 6 transistors, average clock to q delay is given by 8.5ps and finally the power delay product of forced stack with pmos is given by 32.2235aJ.

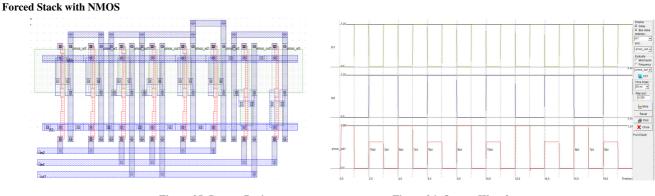

Figure 25: Layout Design

Figure 26: Output Waveform

Figure 25 represents the layout design of forced stack with nmos and figure 26 represents the output simulation waveform of the forced stack with nmos, here total power consumed by the forced stack with nmos is given by  $3.003\mu$ w.For constructing forced stack with nmos we required 5 transistors, average clock to q delay is given by 7.5ps and finally the power delay product of forced stack with nmos is given by 22.5225aJ.

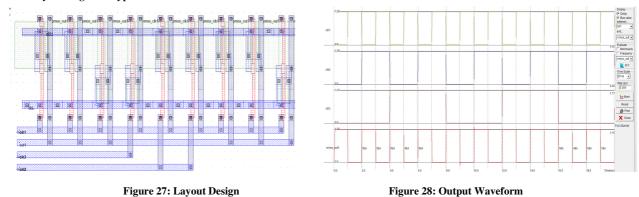

Variable Body Biasing with Bypass

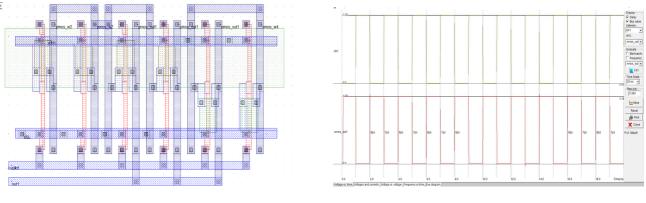

Figure 27 represents the layout design of variable body biasing with bypass and figure 28 represents the output simulation waveform of the variable body biasing with bypass, here total power consumed by the variable body biasing with bypass is given by 0. 35µw.For constructing variable body biasing with bypass we required 6 transistors, average clock to q delay is given by 5ps and finally the power delay product of variable body biasing with bypass is given by 1.777aJ.

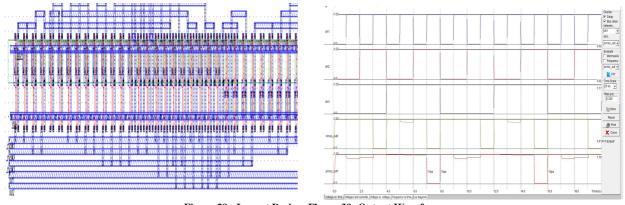

# Full Adder Using Forced Stack

Figure 29 : Layout Design Figure 30: Output Waveform

Figure 29 represents the layout design of full adder using forced stack and figure 30 represents the output simulation waveform of the full adder using forced stack, here total power consumed by the full adder using forced stack is given by 10.686µw.For constructing full adder using forced stack we required 18 transistors, average clock to q delay is given by 15.5ps and finally the power delay product of full adder using forced stack is given by 165.67aJ.

# CONCLUSION

The decline in technology has resulted in increased leak capacity. Today, the leaked power is still much stronger than the Dynamic power current leakage.

The main problem with low power is that digital circuits work very well in CMOS. This article proposes effective ways to reduce existing leaks in VLSI. design. The proposed methods lead to very low power usage with government savings.

The proposed designs have low latency, efficiency, and these strategies work much better than current techniques and have less leaky mechanics. The flexible stem selection system proposed by Bypass is functional and offers a high level of low current power inverter and has the lowest leakage of all the methods discussed in this paper. The results were simulated using the Microwind 3.1 tool in 90nm technology at room temperature.

### **REFER`ENCES**

- Kavali K, Rajendar S, Naresh R. 2015. The design of Low Power Adaptive Pulse TriggeredFlip-Flop Using Modified Clock Gating Schemeat 90nm Technology. Procedia Mater Sci. 10:323–30. DOI: 10.1016/j.mspro.2015.06.063

- Pal PK, Rathore RS, Rana AK, Saini G. 2010. New lowpower techniques: Leakage feedback with stack & sleep stack with the keeper. In: 2010 International Conference on Computer and Communication Technology, ICCCT-2010. IEEE. 296–301.

- 3. Priya MG, Baskaran K, Krishnaveni D. 2012. Leakage power reduction techniques in deep submicron technologies for VLSI applications. Procedia Eng. 30(1):1163–70.

- 4. Rabaey JM. 1996. Digital Integrated Circuits: A Design Perspective. New York (USA); Prentice-Hal

- Fallah F, Pedram M. 2005. Standby and active leakage current control and minimization in CMOS VLSI circuits. IEICE Trans Electron. E88–C (4):509–19.

- Zhou D, Hu J, Wang L. 2007. Adiabatic flip-flops for power-down applications. In: 2007 International Symposium on Integrated Circuits, ISIC. IEEE; 493–6. from

- Zhang W, Su L, Hu J. 2010. Leakage reduction of improved CAL circuits with power-gating schemes. World Acad Sci Eng Technol. 62(1):484– 9. from: http://www.scientific.net/AMR.121-122.281

- Lorenzo, R., & Chaudhury, S. (2013). A Novel all NMOS Leakage Feedback with Data Retention Technique. In Proc. of CARE 2013, IEEE Int. Conference.

- 9. Lorenzo, R., & Chaudhury, S. (2014). Analysis of leakage feedback technique. In Electronics, Communication and Instrumentation (ICECI), 2014 International Conference on. IEEE.

- 10. Sharma, V.K., Pattanaik, M., & Raj, B. (2014). INDEP approach for leakage reduction in CMOS circuits. International Journal of Electronics, 102(1), 200-215.

- 11. Zhu, H., & Kursan, V. (2014). Novel low leakage and high-speed triple threshold voltage buffers with skewed inputs and outputs. IEEE Transactions on Circuits and Systems, (61), 7.

- H. Jeon, Y.-B. Kim and M. Choi, "A novel technique to minimize standby leakage power in nanoscale CMOS VLSI", in Proceedings of the International Instrumentation and Measurement Technology Conference, pp. 1372–1375, 2009.

- Zhu, J., Bai, N., & Wu, J. (2013). A review of sense amplifier for static random-access memory. IETE Technical Review, 30(1), 72–81. doi:10.4103/0256-4602.107343. Masahiro Nomura, et al.," Delay and Power Monitoring Schemes for Minimizing Power Consumption by Means of Supply and Threshold Voltage Control in Active and Standby Modes", IEEE Journal of Solid-State Circuits, Vol.41, No. 4, pp. 805-810, 2006.

- Kyung Ki Kim and Yong-Bin Kim, "A Novel Adaptive Design Methodology for Minimum Leakage Power Considering PVT Variations on Nanoscale VLSI Systems" IEEE Transactions on Very Large-Scale Integrated Systems, Vol. 17, No. 4, pp. 517-528, 2009

- Butzen PF, da Rosa Jr LS, Chiappetta Filho EJ, Reis AI, Ribas RP (2010) Standby power consumption estimation by interacting leakage current mechanisms in nanoscaled CMOS digital circuits. Microelectron J 41(4):247–255

- Faraji R, Hamid Reza N, Majid Rahimi N, Mohammad A (2013) New SRAM design using body bias technique for low-power and high-speed applications. Int J Circuit Theory Appl 42(11):1189–1202

- 17. Sharma VK, Pattanaik M, Raj B (2014) ONOFIC approach: low power high speed nanoscale VLSI circuits design. Int J Electron 101(1):61–73 (Taylor and Francis)

- 18. Sharma VK, Pattanaik M, Raj B (2015) INDEP approach for leakage reduction in nanoscale CMOS circuits. Int J Electron 102(2):200–215 (Taylor and Francis)

- Lorenzo, R., Chaudhury, S. LCNT-an approach to minimize leakage power in CMOS integrated circuits. Microsyst Technol 23, 4245–4253 (2017). https://doi.org/10.1007/s00542-016-2996-y

- Schwantes S, Krautschneider W. Relevance of gate current for the functionality of deep submicron CMOS circuits. InEuropean Solid-State Device Research Conference (ESSDERC 2001), Nuremberg, Germany, Sept. 11–13, 2001, pp. 471–474.

- Dongwoo Lee, Wesley Kwong, David Blaauwet al. Simultaneous subthreshold and gate-oxide tunneling leakage current analysis in nanometer CMOS design. In4th International Symposium on Quality Electronic Design (ISQED 2003), March 24–26, 2003, San Jose, California, pp.287– 292.

- Dongwoo Lee, Wesley Kwong, David Blaauwet al. Analysis and minimization techniques for total leakage considering gate oxide leakage. Design Automation Conference (DAC 2003), June 2–6, 2003. Anaheim, California, USA, pp.175–180.

- Wenjie Jiang, Vivek Tiwari, Erik de la Iglesiaet al. Topological analysis for leakage prediction of digital circuits. InProc. the Asia and South Pacific Design Automation Conference and International Conference on VLSI Design (ASPDAC 2002 & VLSI Design 2002), Bangalore, India, 2002, pp.39–44.

- 24. http://www.erc.msstate.edu/mpl/distributions/scmos/ scmos\_doc/index.html

- 25. Prasad Subramanian, "Power management for optimal power design", ESILICON, Corp.2010

- A.Tonk, "A Literature Review on Leakage and Power Reduction Techniques in CMOS VLSI Design", International Journal on Recent and Innovation Trends in Computing and Communication, vol. 3, no. 2, pp. 554-558, 2015.