### International Journal of Research Publication and Reviews

Journal homepage: www.ijrpr.com ISSN 2582-7421

# Adaptive Noise Filtering based Design of Analog to Digital Converters

## <sup>1</sup>Sourabh Yadav, <sup>2</sup>Prof.Mukta Sahu

<sup>1</sup>Mtech scholar, Department of ECE Engineering, LNCT (Bhopal) Indore Campus (old name:- Lord Krishna college of technology, Indore)

<sup>2</sup>Asst. professor, Dept. of ECE Engineering, LNCT (Bhopal) Indore Campus (old name: - Lord Krishna college of technology, Indore)

#### ABSTRACT:

The design for analog to digital converters has grown rapidly as most of the systems have migrated from analog to digital functioning. In this paper, a multi-stage noise-shaping (MASH) type analog to digital converter has been proposed with adaptive noise shaping. The evaluation of the proposed system has been done based on the signal to noise ratio of the system. It has been shown that the signal to noise ratio increases with the increase in the oversampling ratio as well as the number of stages. To evaluate the stability of the MASH conversion, the pole zero plot for the system has also been plotted. It has been found that as the number of levels or order of the MASH ADC increases beyond four, the system tends to become unstable thereby making the system unstable.

Keywords: Analog to Digital conversion, MASH ADC, Oversampling Ratio, Signal to Noise Ratio.

#### INTRODUCTION

Almost all practical electronics systems have migrated towards digital owing to the noise immunity of digital systems. However, most of the practical signals encountered in real life are analog in nature. Therefore, a fundamental necessity to convert signals from analog to digital is of primary and fundamental importance. This makes the design of analog to digital converters critically important. The analog to digital conversion process ins inherently prone to errors due to the following reasons:

- 1) Information loss due to anti-aliasing filters to mitigate the limitations of practical sample and hold circuits.

- 2) Quantization error occurring due to the quantization process.

For instance, if the maximum signal frequency is 50kHz and the limit of the sample to hold circuit is 80KHz, then the following aliasing needs to be made.

$$X(t)_{t-d} \underset{FT}{\rightarrow} X(f)_{f-d}$$

If.

$$f_{max} = 50kHz$$

Adhering to Shannon's theorem,

$$f_s \geq 2 * f_{max}$$

Thus in this case,

$$f_{max} = 2 * 50 = 100kHz$$

Due to the limit of the sample and hold circuit being 80kHz, an anti alias filter with a cut off need to be designed. The cut off the anti-alias filter can be computed as:

$$f_{cut-off} = \frac{AAF_{limit}}{2}$$

Here

x(t) denote the time domain signal.

X(f) denotes the frequency domain signal.

FT represents the Fourier Transform.

$f_{max}$  denotes the maximum frequency of the analog signal.

t-d represents time domain.

f-d represents frequency domain.

$f_{cut-off}$  represents the cut-off frequency of the AAF.

$AAF_{limit}$  represents the limit of the anti-alias filer.

Thus, the part of the frequency domain exceeding the cut-off of the sample and hold circuit needs to be stripped from the signal which is a basic limitation of the sampling and hold circuit. Thus the information content in the signal in the band between the cut-off of the AAF and the limit of the sampling and hold circuit. Thus the information loss occurs in the frequency range of:

$$f_{loss} = f_{max} - f_{cut-off}$$

Here,

$f_{loss}$  denotes the loss band of the signal.

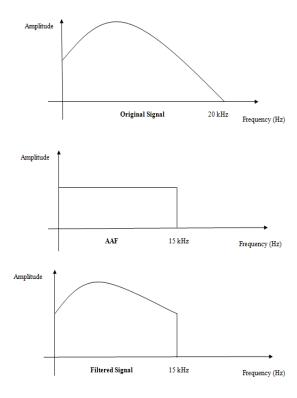

The entire process is depicted in figure 1. The loss in the loss band in irrecoverable and causes noise or errors in the final version of the analog signal when converted from digital to analog.

Fig.1 Illustration of the information loss due to AAF.

The other type of loss occurs due to the approximations in the quantization process which is mandatory for analog to digital conversion. For instance, if the quantization threshold is set in between the lower and higher limits of the signal amplitude swing, then the quantization error can be computed as:

$$Thresh_L = k1$$

$$Thresh_H = k2$$

$$Q_{Thresh} = \frac{k1 - k2}{2}$$

The maximum quantization noise in this case would be given by:

$$Qe_{Max} = \frac{\Delta}{2}$$

Here,

$Qe_{Max}$  denotes the maximum quantization noise.

$\boldsymbol{\Delta}$  represents the signal amplitude swing.

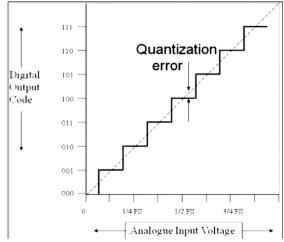

The occurrence of the quantization error as a function of the signal values are depicted in figure 2.

Fig.2Variation of Quantisation error as a function of signal voltage

From the previous discussions, it is clear that the noise in the system is inherent and additional measures need to be taken in conjugation with analog to digital conversion process so as to reduce the error and noise effects.

#### SYSTEM DESIGN

The system design of the proposed system is based on the estimation of the embedded noise in the system and them formulating a mechanism to estimate the noise transfer function (NTF). The mathematical formulation of the system design is given by:

$$N_{est}^1 = y_o^1 - y_i$$

Here

$N_{est}^1$  represents the estimated noise for stage 1 of the MASH ADC.

$y_o^1$  is the output of the first stage of the MASH ADC.

$y_i$  is the actual input to the ADC.

The estimation of the noise can be done recursively till the noise is within the noise threshold or the stability of the system becomes marginal, i.e.

```

for(i=1, i \leq n, i=i+1) { estimate\ N_{est}^n\ as\ y_o^n - y_i Obtain\ NTF\ as: NTF(\omega) = \underset{F.T.(\omega)}{\longrightarrow} N_{est}^n(t) }

```

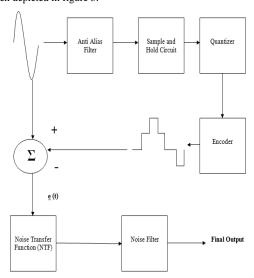

The design of multi stage analog to digital conversion process relies on the noise shaping or noise estimation subsequent to each stage. The noise in each stage is estimated using a feedback look to compute the difference between the actual and the processing signal by the ADC. The signal to noise ratio has to be varied in accordance with the number of stages (or order) of the analog to digital converter and the oversampling ratio. The block level implementation of the proposed system has been depicted in figure 3.

Fig.3Block Level Implementation of Proposed System.

The performance of the system is evaluated in terms of the signal to noise ratio which is again a function of the order of the MASH as well as the oversampling ratio of the MASH at a particular order. Mathematically,

SNR = f(O, L)

Here,

SNR stands for signal to noise ratio.

f stands for a function

O stands for oversampling ratio

L stands for present MASH order.

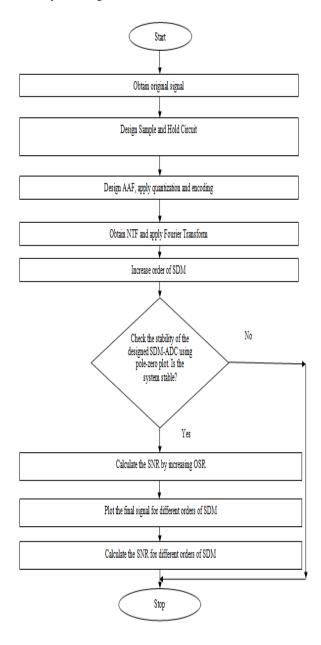

The flowchart of the proposed system has been depicted in figure 4.

Fig.4: Flow Chart for Proposed System

### EXPERIMENTAL RESULTS

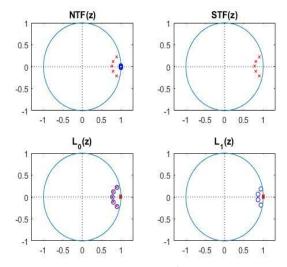

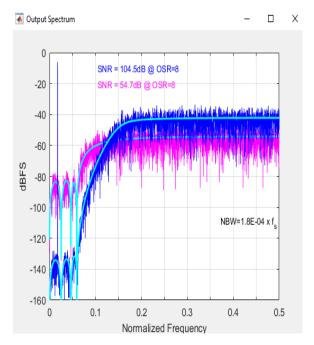

The performance of the proposed system has bene evaluated in terms of the SNR varying in accordance with the oversampling ratio and the order of the MASH. The stability analysis has been done based on the pole zero plot of the system.

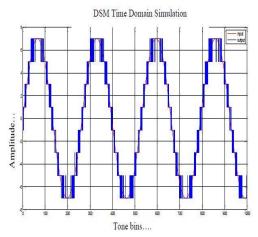

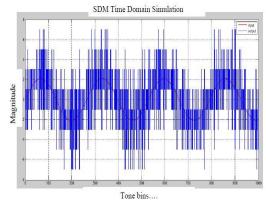

Fig.5First order t-d response

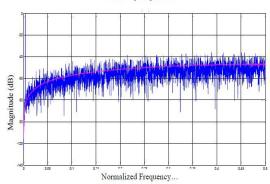

Fig.6First order f-d response

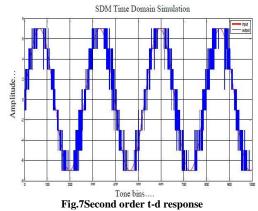

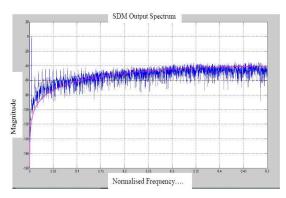

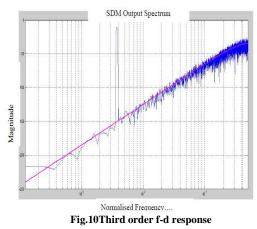

Fig.8Second order f-d response

Fig.9Third order t-d response

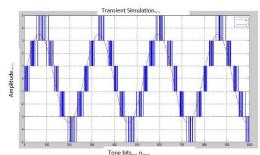

Fig.11Fourth order t-d response

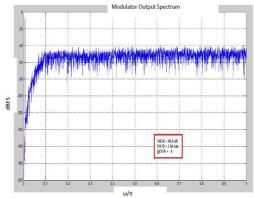

$Fig. 12 Fourth\ order\ f-d\ response$

Fig.13 P-Z Plot for 5<sup>th</sup> order

Fig.14Gain plot for  $5^{th}$  order

Fig.15SNR as a function of OSR

Table.1 Comparative SNR-OSR Analysis for different SDM Levels

| S.No. | SDM-Order | OSR | SNR   |

|-------|-----------|-----|-------|

| 1     | 1         | 2   | 23.43 |

| 2     | 1         | 4   | 31.46 |

| 3     | 1         | 8   | 38.55 |

| 4     | 1         | 16  | 47.11 |

| 5     | 1         | 32  | 56.08 |

| 6     | 2         | 2   | 24.85 |

| 7     | 2         | 4   | 32.64 |

| 8     | 2         | 8   | 39.33 |

| 9     | 2         | 16  | 49.77 |

| 10    | 2         | 32  | 58.25 |

| 11    | 3         | 2   | 26.88 |

| 12    | 3         | 4   | 39.49 |

| 13    | 3         | 8   | 50.60 |

| 14    | 3         | 16  | 70.22 |

| 15    | 3         | 32  | 93.08 |

| 16    | 4         | 2   | 28.1  |

| 17    | 4         | 4   | 48.8  |

| 18    | 4         | 8   | 55.7  |

| 19    | 4         | 16  | 77.1  |

| 20    | 4         | 32  | 104.5 |

The table above depicts the variation of the SNR values with the variation of the OSR values for orders of the MASH.

#### **CONCLUSION**

It can be concluded from the previous discussions that almost all practical electronics systems have migrated towards digital owing to the noise immunity of digital systems. However, most of the practical signals encountered in real life are analog in nature. Therefore, a fundamental necessity to convert signals from analog to digital is of primary and fundamental importance. This makes the design of analog to digital converters critically important. In this paper, a multi-stage noise-shaping (MASH) type analog to digital converter has been proposed with adaptive noise shaping. The evaluation of the proposed system has been done based on the signal to noise ratio of the system.

#### REFERENCES

- [1] S. Oh et al., "A 80dB DR 6MHz Bandwidth Pipelined Noise-Shaping SAR ADC with 1–2 MASH structure," 2020 IEEE Custom Integrated Circuits Conference (CICC), 2020, pp. 1-4, doi: 10.1109/CICC48029.2020.9075929

- [2] M. Akbari, M. Honarparvar, Y. Savaria and M. Sawan, "OTA-Free MASH Two-Step Incremental ADC based on Noise Shaping SAR ADCs," 2020 18th IEEE International New Circuits and Systems Conference (NEWCAS), 2020, pp. 138-141, doi: 10.1109/NEWCAS49341.2020.9159802.

- [3] M. Akbari, M. Honarparvar, Y. Savaria and M. Sawan, "OTA-Free MASH 2–2 Noise Shaping SAR ADC: System and Design Considerations," 2020 IEEE International Symposium on Circuits and Systems (ISCAS), 2020, pp. 1-5, doi: 10.1109/ISCAS45731.2020.9180832

- [4] M. Akbari, M. Honarparvar, Y. Savaria and M. Sawan, "Power Bound Analysis of a Two-Step MASH Incremental ADC Based on Noise-Shaping SAR ADCs," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 8, pp. 3133-3146, Aug. 2021, doi: 10.1109/TCSI.2021.3077366.

- [5] H. Maghami et al., "A Highly Linear OTA-Free VCO-Based 1-1 MASH \$\Delta\Sigma\$ ADC," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 7, pp. 2440-2453, July 2019, doi: 10.1109/TCSI.2019.2897785.

- [6] M. Sadollahi and G. C. Temes, "A 10-MHz BW 77.9 dB SNDR DT MASH \$\Delta\\\\Sigma\$ ADC With NC-VCO-Based Quantizer and OPAMP Sharing," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 9, pp. 3384-3392, Sept. 2019, doi: 10.1109/TCSI.2019.2928591.

- [7] D. Li et al., "High Resolution ADC for Ultrasound Color Doppler Imaging Based on MASH Sigma-Delta Modulator," in IEEE Transactions on Biomedical Engineering, vol. 67, no. 5, pp. 1438-1449, May 2020, doi: 10.1109/TBME.2019.2938275.

- [8] H. Maghami et al., "A Highly Linear OTA-Less 1-1 MASH VCO-Based \$\Delta\Sigma\$ ADC With an Efficient Phase Quantization Noise Extraction Technique," in IEEE Journal of Solid-State Circuits, vol. 55, no. 3, pp. 706-718, March 2020, doi: 10.1109/JSSC.2019.2954764.

- [9] Y. Song, Y. Zhu, C. Chan, L. Geng and R. P. Martins, "A 77dB SNDR 12.5MHz Bandwidth 0–1 MASH  $\Sigma\Delta$  ADC Based on the Pipelined-SAR Structure," 2018 IEEE Symposium on VLSI Circuits, 2018, pp. 203-204, doi: 10.1109/VLSIC.2018.8502382.

- [10] C. Han, B. Park and N. Maghari, "Can SMASH Smash MASH?," 2018 IEEE International Symposium on Circuits and Systems (ISCAS), 2018, pp. 1-5, doi: 10.1109/ISCAS.2018.8351710.

- [11] E. Gutierrez, L. Hernandez, S. Paton and P. Rombouts, "Optimal NTF zero placement in MASH VCO-ADCs with higher order noise shaping," 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2018, pp. 805-808, doi: 10.1109/ICECS.2018.8617937.

- [12] Y. Kwak, K. Cho, H. Kim, S. Lee and G. Ahn, "A 72.9-dB SNDR 20-MHz BW 2-2 Discrete-Time Resolution-Enhanced Sturdy MASH Delta–Sigma Modulator Using Source-Follower-Based Integrators," in IEEE Journal of Solid-State Circuits, vol. 53, no. 10, pp. 2772-2782, Oct. 2018, doi: 10.1109/JSSC.2018.2859401.

- [13] K. Seo, I. Jang, K. Noh and S. Ryu, "An incremental zoom sturdy MASH ADC," 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS), 2017, pp. 1013-1016, doi: 10.1109/MWSCAS.2017.8053098.

- [14] L. C. Gunnam, G. Sung and L. Weng, "2+1- order Switched-current MASH Delta-Sigma ADC with the digital cancellation circuit," 2017 International Conference on Applied System Innovation (ICASI), 2017, pp. 1801-1804, doi: 10.1109/ICASI.2017.7988293.

- [15] E. Gutierrez, L. Hernandez, F. Cardes and P. Rombouts, "A Pulse Frequency Modulation Interpretation of VCOs Enabling VCO-ADC Architectures With Extended Noise Shaping," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 65, no. 2, pp. 444-457, Feb. 2018, doi: 10.1109/TCSI.2017.2737830.